CY22701 Overview

Key Specifications

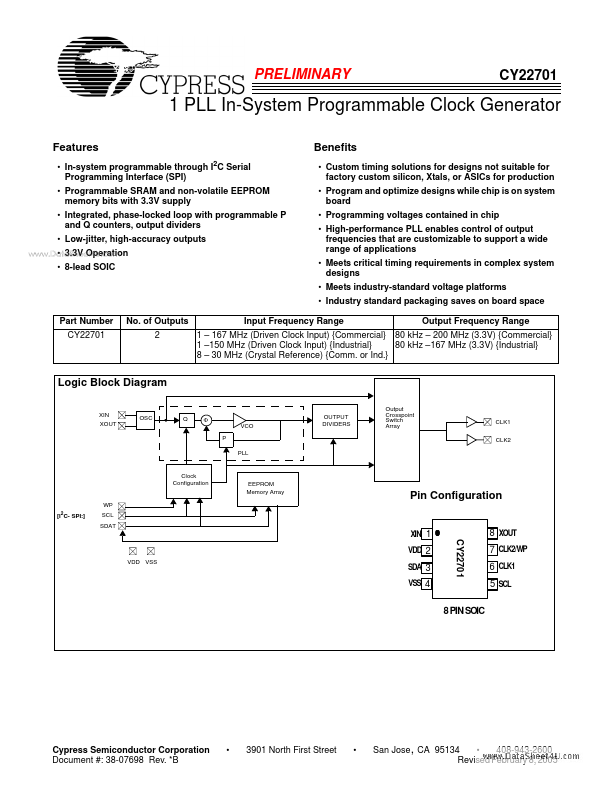

Package: SOIC

Pins: 8

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Key Features

- In-system programmable through I2C Serial Programming Interface (SPI)

- Programmable SRAM and non-volatile EEPROM memory bits with 3.3V supply

- Integrated, phase-locked loop with programmable P and Q counters, output dividers

- Low-jitter, high-accuracy outputs

- 3.3V Operation