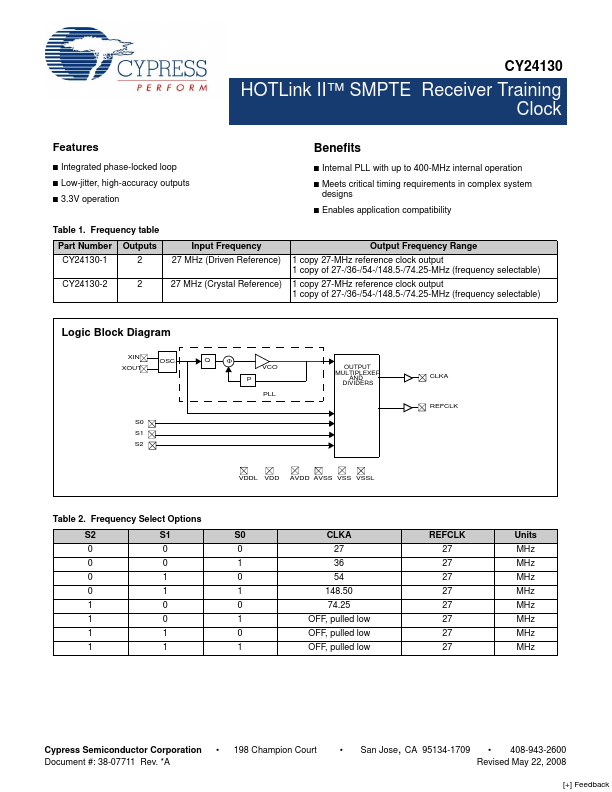

CY24130 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 3.3 V

Key Features

- Integrated phase-locked loop

- Low-jitter, high-accuracy outputs

- 3.3V operation

- Internal PLL with up to 400-MHz internal operation

- Meets critical timing requirements in complex system designs