CY28442

CY28442 is Clock Generator manufactured by Cypress.

..

ADVANCE INFORMATION

Clock Generator for Intel Alviso Chipset

Features

- pliant to Intel CK410M

- Supports Intel Pentium-M CPU

- Selectable CPU frequencies

- Differential CPU clock pairs

- 100-MHz differential SRC clocks

- 96-MHz differential dot clock

- 48-MHz USB clocks

- SRC clocks independently stoppable through CLKREQ#[A:B]

- 96/100 MHz Spreadable differential clock.

- 33-MHz PCI clock

- Low-voltage frequency select input

- I2C support with readback capabilities

- Ideal Lexmark Spread Spectrum profile for maximum electromagnetic interference (EMI) reduction

- 3.3V power supply

- 56-pin TSSOP package

CPU x2 / x3 SRC x5/6 PCI x6 REF x2 DOT96 x2 USB_48 x1

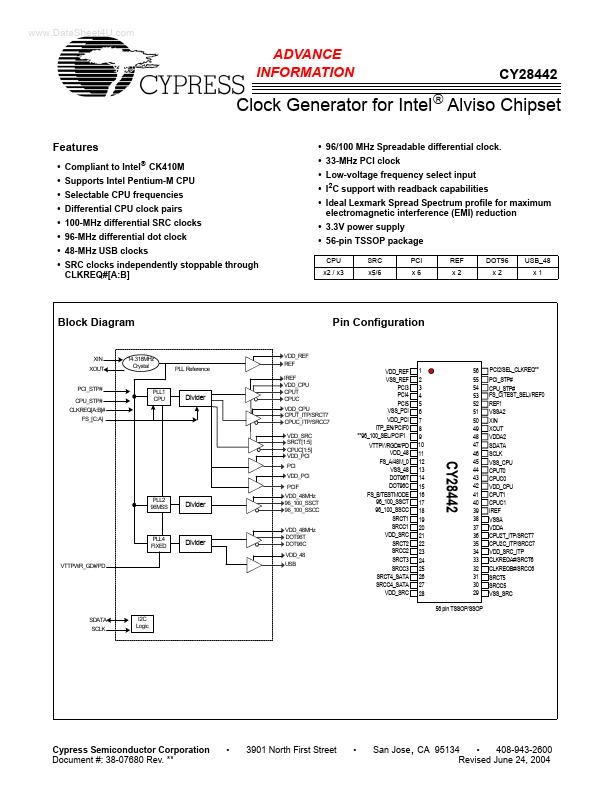

Block Diagram

VDD_REF REF IREF VDD_CPU CPUT CPUC VDD_CPU CPUT_ITP/SRCT7 CPUC_ITP/SRCC7 VDD_SRC SRCT[1:5] CPUC[1:5] VDD_PCI PCI VDD_PCI PCIF PLL2 96MSS VDD_48MHz 96_100_SSCT 96_100_SSCC VDD_48MHz DOT96T DOT96C VDD_48 VTTPWR_GD#/PD USB

Pin Configuration

XIN XOUT PCI_STP# CPU_STP# CLKREQ[A:B]# FS_[C:A]

14.318MHz Crystal

PLL Reference

PLL1 CPU

Divider

Divider

PLL4...