CY2SSTU877

CY2SSTU877 is 10-Output JEDEC-Compliant Zero Delay Buffer manufactured by Cypress.

..

PRELIMINARY

1.8V, 500-MHz, 10-Output JEDEC-pliant Zero Delay Buffer

Features

- Operating frequency: 125 MHz to 500 MHz

- Supports DDRII SDRAM

- Ten differential outputs from one differential input

- Spread-Spectrum-patible

- Low jitter (cycle-to-cycle): < 40 ps

- Very low skew: < 40 ps

- Power management control input

- 1.8V operation

- Fully JEDEC-pliant

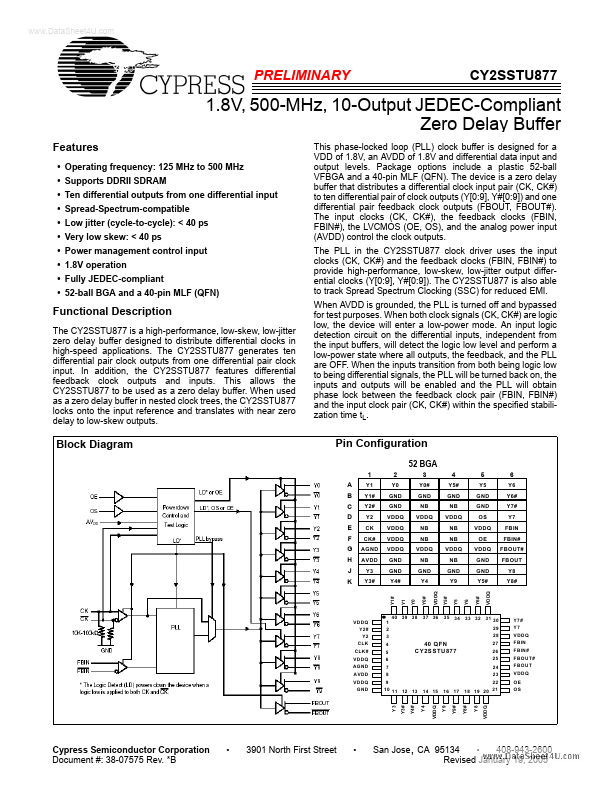

- 52-ball BGA and a 40-pin MLF (QFN) This phase-locked loop (PLL) clock buffer is designed for a VDD of 1.8V, an AVDD of 1.8V and differential data input and output levels. Package options include a plastic 52-ball VFBGA and a 40-pin MLF (QFN). The device is a zero delay buffer that distributes a differential clock input pair (CK, CK#) to ten differential pair of clock outputs (Y[0:9], Y#[0:9]) and one differential pair feedback clock outputs (FBOUT, FBOUT#). The input clocks (CK, CK#), the feedback clocks (FBIN, FBIN#), the LVCMOS (OE, OS), and the analog power input (AVDD) control the clock outputs. The PLL in the CY2SSTU877 clock driver uses the input clocks (CK, CK#) and the feedback clocks (FBIN, FBIN#) to provide high-performance, low-skew, low-jitter output differential clocks (Y[0:9], Y#[0:9]). The CY2SSTU877 is also able to track Spread Spectrum Clocking (SSC) for reduced EMI. When AVDD is grounded, the PLL is turned off and bypassed for test purposes. When both clock signals (CK, CK#) are logic low, the device will enter a low-power mode. An input logic detection circuit on the differential inputs, independent from the input buffers, will detect the logic low level and perform a low-power state where all outputs, the feedback, and the PLL are OFF. When the inputs transition from both being logic low to being differential signals, the PLL will be turned back on, the inputs and outputs will be enabled and the PLL will obtain phase lock between the feedback clock pair (FBIN, FBIN#) and the input clock pair (CK, CK#) within the specified stabilization time t...