CY2SSTV16859

Description

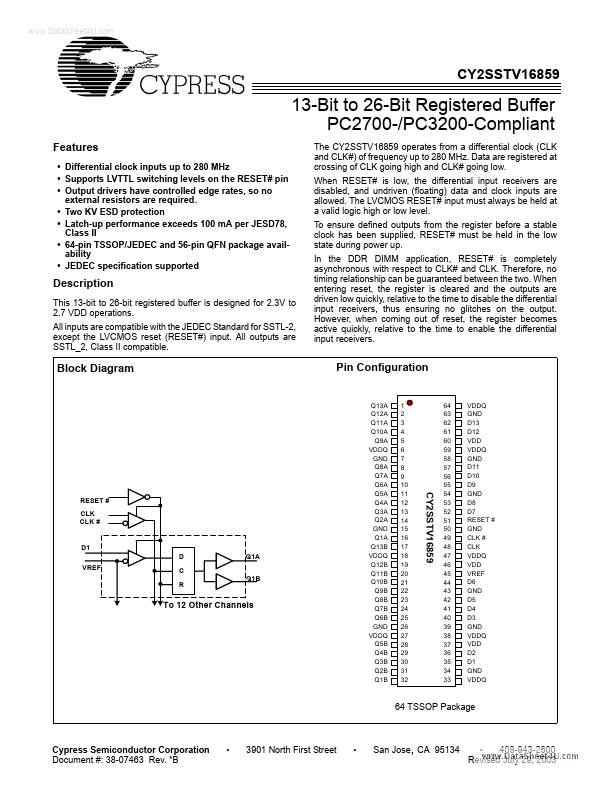

This 13-bit to 26-bit registered buffer is designed for 2.3V to 2.7 VDD operations.

Key Features

- Differential clock inputs up to 280 MHz

- Supports LVTTL switching levels on the RESET# pin

- Output drivers have controlled edge rates, so no external resistors are required

- Two KV ESD protection

- Latch-up performance exceeds 100 mA per JESD78, Class II

- 64-pin TSSOP/JEDEC and 56-pin QFN package availability