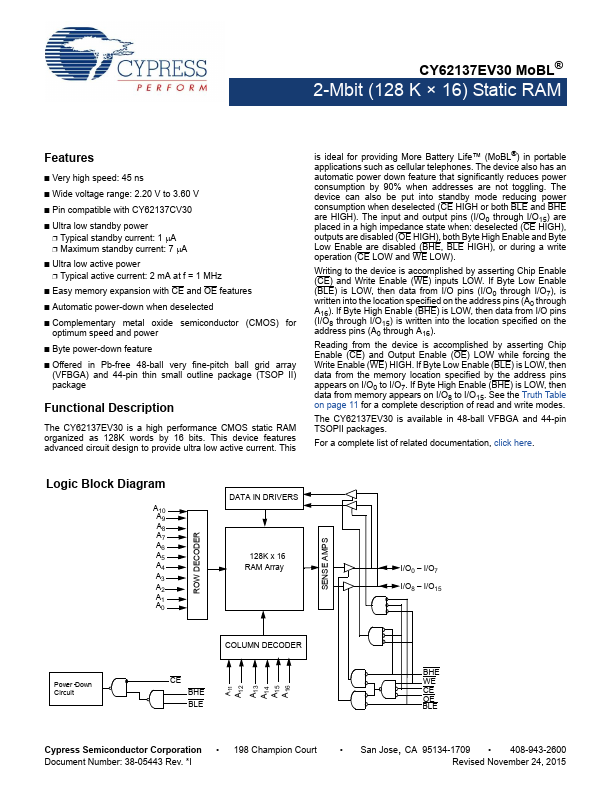

CY62137EV30 Overview

Key Specifications

Package: TSOP

Mount Type: Surface Mount

Pins: 44

Operating Voltage: 3 V

Key Features

- Very high speed: 45 ns

- Wide voltage range: 2.20 V to 3.60 V

- Pin compatible with CY62137CV30

- Ultra low standby power ❐ Typical standby current: 1 A ❐ Maximum standby current: 7 A

- Ultra low active power ❐ Typical active current: 2 mA at f = 1 MHz