CY7C016

Features

- True dual-ported memory cells which allow simultaneous reads of the same memory location

- 16K x 8 organization (CY7C006)

- 16K x 9 organization (CY7C016)

- 0.65-micron CMOS for optimum speed/power

- High-speed access: 15 ns

- Low operating power: ICC = 140 m A (typ.)

- Fully asynchronous operation

- Automatic power-down

- TTL patible

- Expandable data bus to 16/18 bits or more using Master/Slave chip select when using more than one device

- Busy arbitration scheme provided

- Semaphores included to permit software handshaking between ports

- INT flag for port-to-port munication

- Available in 68-pin PLCC (7C006), 64-pin (7C006) and 80-pin (7C016) TQFP

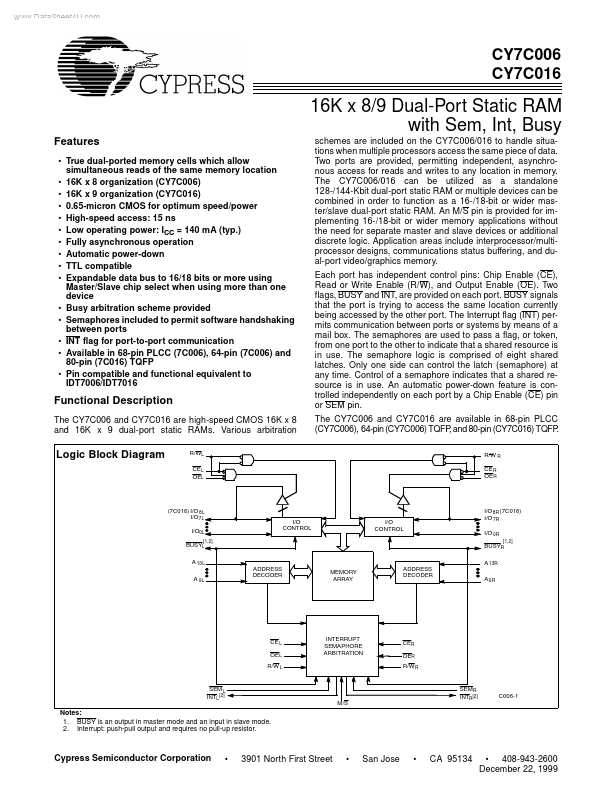

- Pin patible and functional equivalent to IDT7006/IDT7016 schemes are included on the CY7C006/016 to handle situations when multiple processors access the same piece of data. Two ports are provided, permitting independent, asynchronous access for reads and writes to any location in memory. The CY7C006/016 can be utilized as a...