CY7C09389 Overview

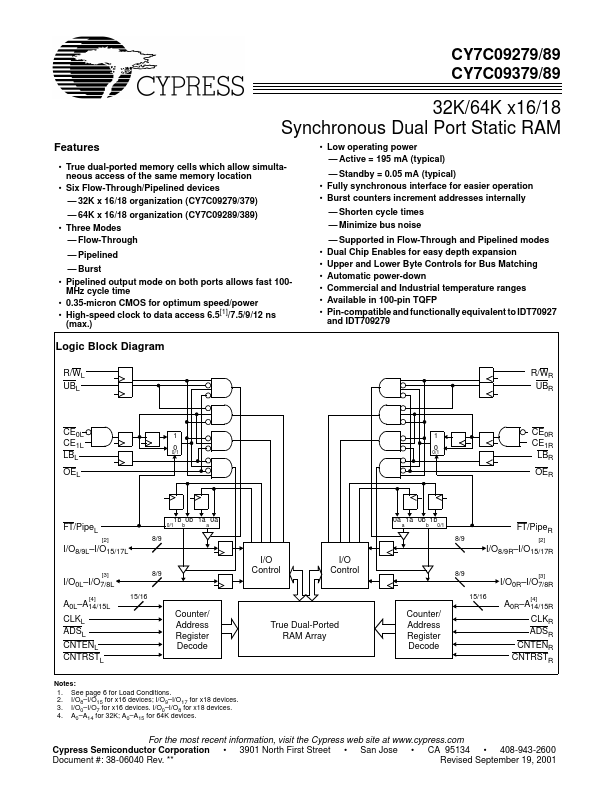

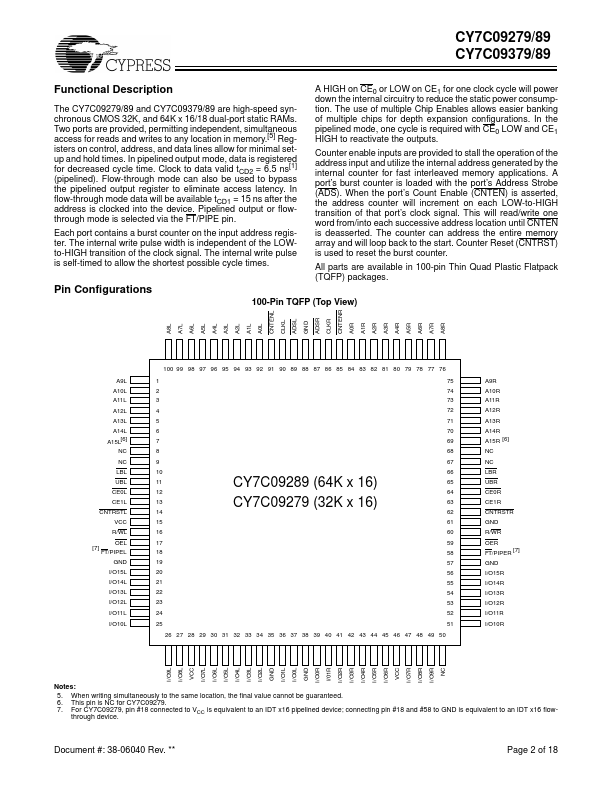

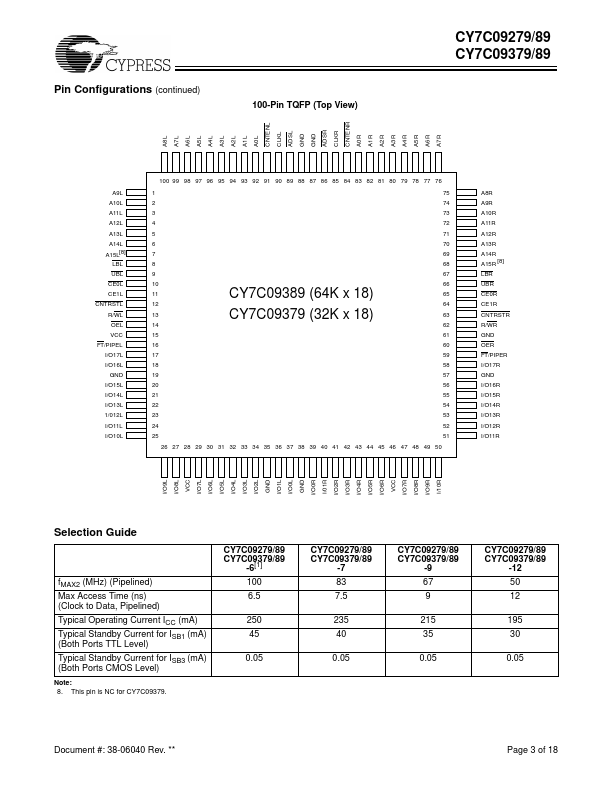

Two ports are provided, permitting independent, simultaneous access for reads and writes to any location in memory.[5] Registers on control, address, and data lines allow for minimal setup and hold times. In pipelined output mode, data is registered for decreased cycle time. Clock to data valid tCD2 = 6.5 ns[1] (pipelined).

CY7C09389 Key Features

- True dual-ported memory cells which allow simultaneous access of the same memory location

- Six Flow-Through/Pipelined devices

- 32K x 16/18 organization (CY7C09279/379)

- 64K x 16/18 organization (CY7C09289/389)

- Three Modes

- Flow-Through

- Pipelined

- Pipelined output mode on both ports allows fast 100MHz cycle time

- 0.35-micron CMOS for optimum speed/power

- High-speed clock to data access 6.5[1]/7.5/9/12 ns (max.)