CY7C1061DV18

Overview

- High Speed ❐ tAA = 15 ns

- Low Active Power ❐ ICC = 150 mA at 67 MHz

- Low complementary metal oxide semiconductor (CMOS) Standby Power ❐ ISB2 = 25 mA

- Operating voltages of 1.7 V to 2.2 V

- 1.5 V data retention

- Automatic power-down when deselected

- Transistor-transistor logic (TTL) compatible inputs and outputs

- Easy memory expansion with CE1 and CE2 features

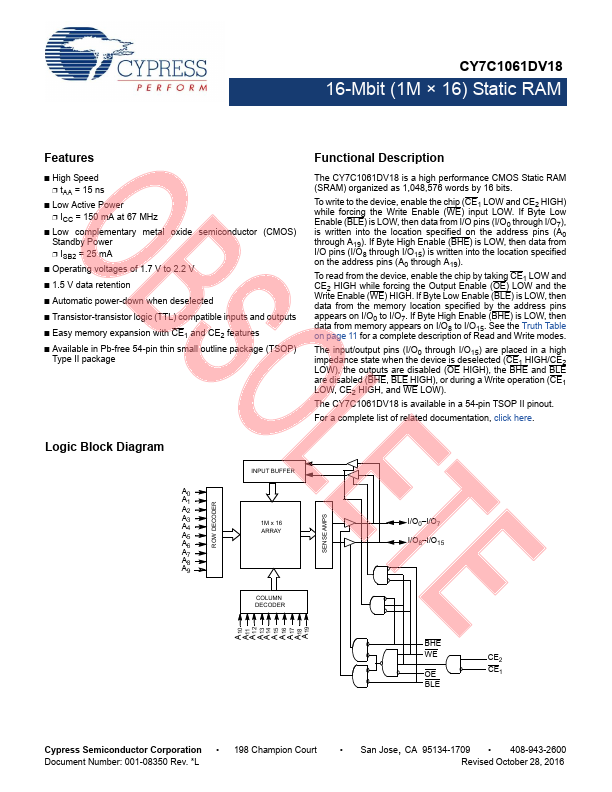

- Available in Pb-free 54-pin thin small outline package (TSOP) Type II package Functional Description The CY7C1061DV18 is a high performance CMOS Static RAM (SRAM) organized as 1,048,576 words by 16 bits. To write to the device, enable the chip (CE1 LOW and CE2 HIGH) while forcing the Write Enable (WE) input LOW. If Byte Low Enable (BLE) is LOW, then data from I/O pins (I/O0 through I/O7), is written into the location specified on the address pins (A0 through A19). If Byte High Enable (BHE) is LOW, then data from I