CY7C1062DV33 Overview

Key Features

- High speed ❐ tAA = 10 ns

- Low active power ❐ ICC = 175 mA at 10 ns

- Low complementary metal oxide semiconductor (CMOS) standby power ❐ ISB2 = 25 mA

- Operating voltages of 3.3 ± 0.3 V

- 2.0 V data retention

- Automatic power down when deselected

- Transistor-transistor logic (TTL) compatible inputs and outputs

- Easy memory expansion with CE1, CE2, and CE3 features

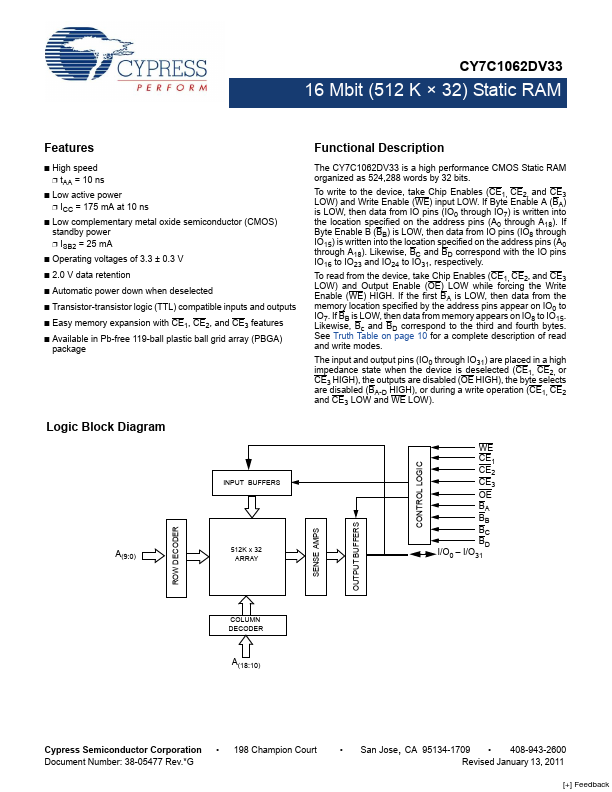

- Available in Pb-free 119-ball plastic ball grid array (PBGA) package Logic INPUT BUFFERS A(9:0) 512K x 32 ARRAY