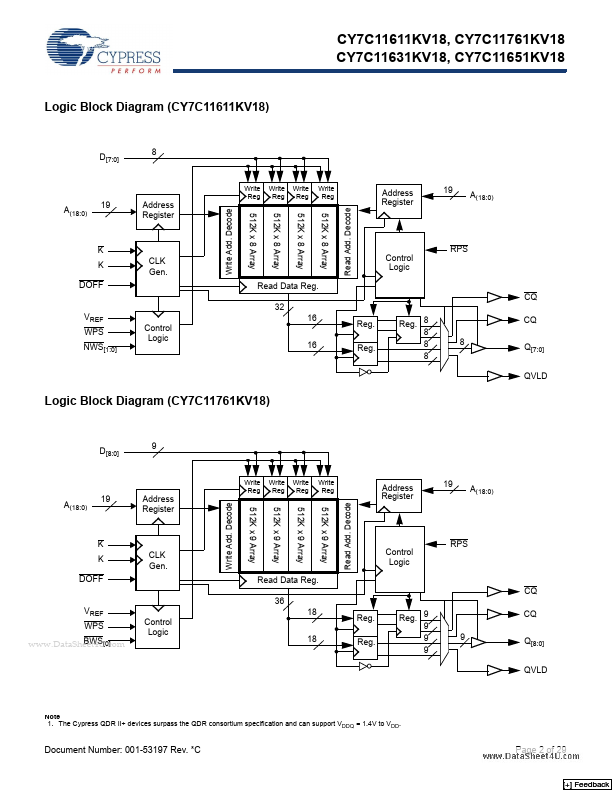

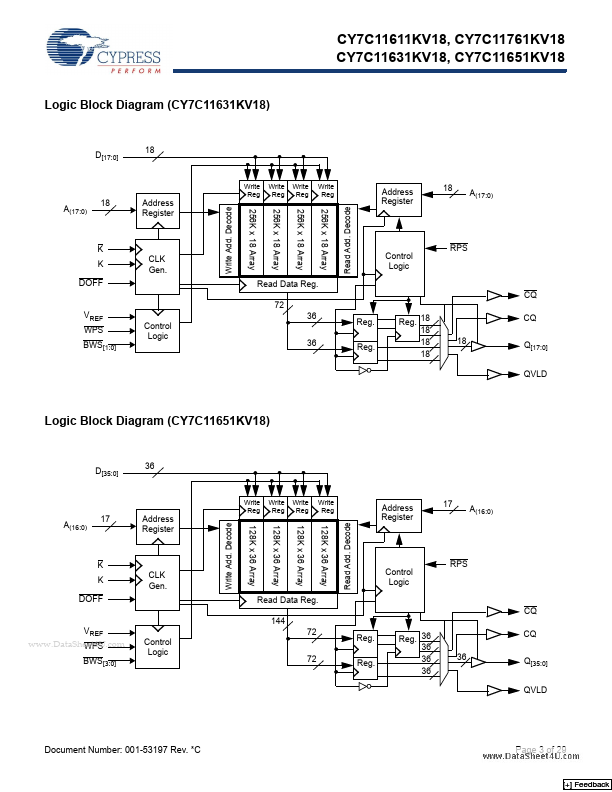

CY7C11611KV18 Description

Similar to QDR II architecture, QDR II+ architecture consists of two separate ports: the read port and the write port to access the memory array. The read port has dedicated data outputs to support read operations and the write port has dedicated data inputs to support write operations.

CY7C11611KV18 Key Features

- Supports concurrent transactions 550 MHz clock for high bandwidth 4-word burst for reducing address bus frequency Double

- SRAM uses rising edges only Echo clocks (CQ and CQ) simplify data capture in high speed systems Data valid pin (QVLD) to