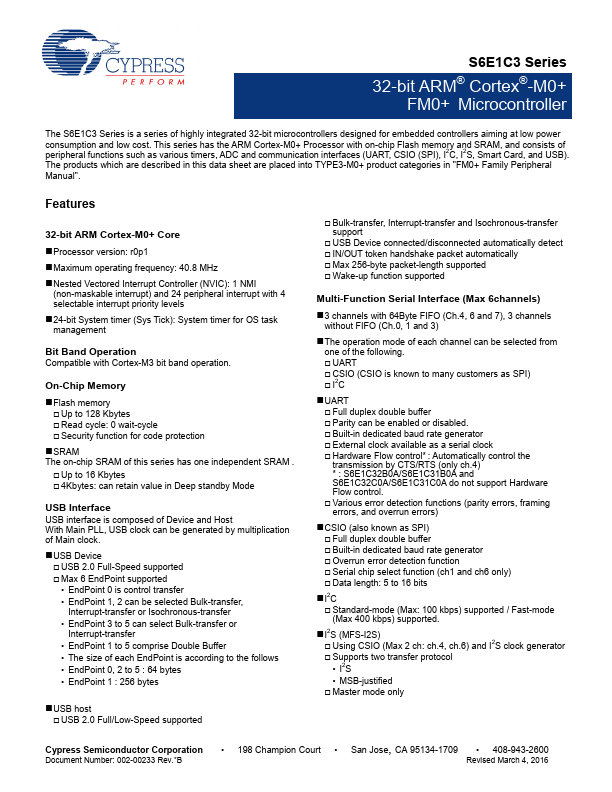

S6E1C32C0A Overview

Key Specifications

Package: LFQFP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 1.65 V

Key Features

- Processor version: r0p1

- Maximum operating frequency: 40.8 MHz

- Flash memory Up to 128 Kbytes Read cycle: 0 wait-cycle Security function for code protection

- USB Device USB 2.0 Full-Speed supported Max 6 EndPoint supported

- EndPoint 0 is control transfer