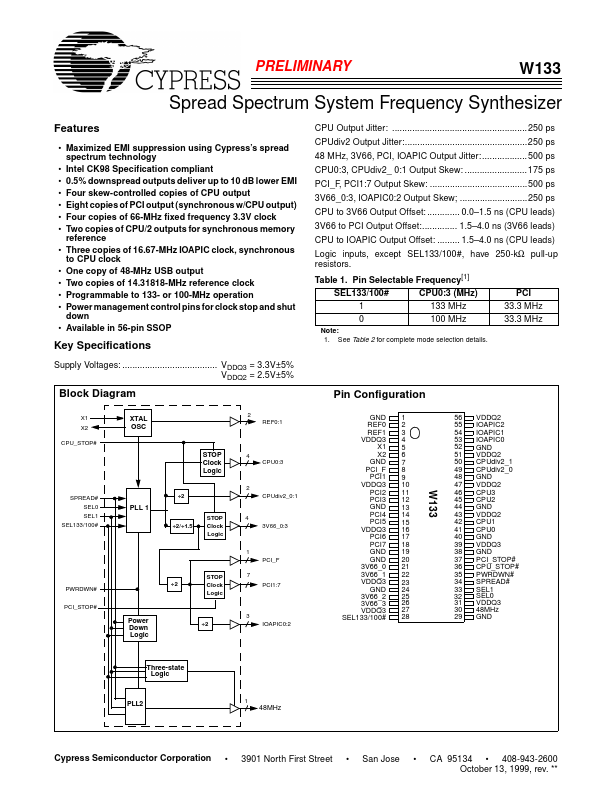

W133

Key Features

- Maximized EMI suppression using Cypress’s spread spectrum technology

- Intel CK98 Specification pliant

- 0.5% downspread outputs deliver up to 10 dB lower EMI

- Four skew-controlled copies of CPU output

- Eight copies of PCI output (synchronous w/CPU output)

- Four copies of 66-MHz fixed frequency 3.3V clock

- Two copies of CPU/2 outputs for synchronous memory reference

- Three copies of 16.67-MHz IOAPIC clock, synchronous to CPU clock

- One copy of 48-MHz USB output

- Two copies of 14.31818-MHz reference clock