CY7C4804V25 Description

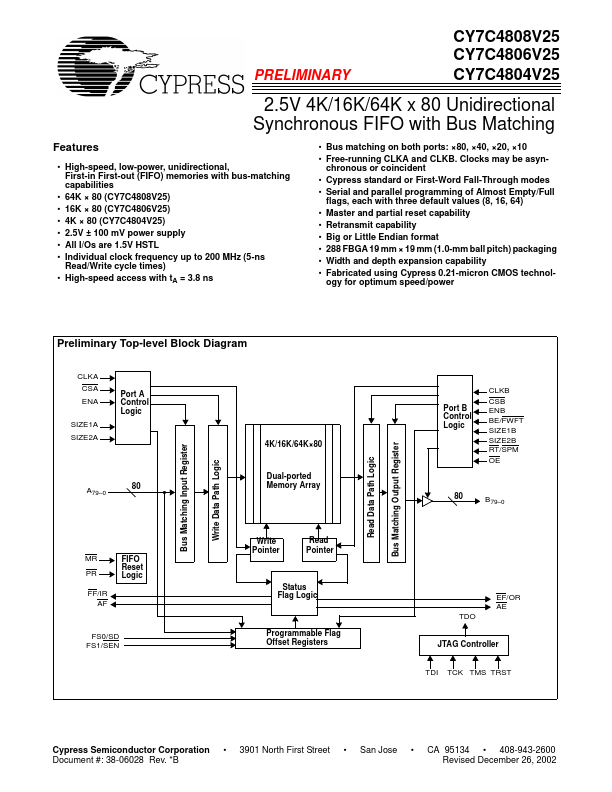

sure C025/0251 PRELIMINARY CY7C4808V25 CY7C4806V25 CY7C4804V25 2.5V 4K/16K/64K x 80 Unidirectional Synchronous FIFO with Bus.

CY7C4804V25 Key Features

- High-speed, low-power, unidirectional, First-in First-out (FIFO) memories with bus-matching capabilities

- 64K × 80 (CY7C4808V25)

- 16K × 80 (CY7C4806V25)

- 4K × 80 (CY7C4804V25)

- 2.5V ± 100 mV power supply

- All I/Os are 1.5V HSTL

- Individual clock frequency up to 200 MHz (5-ns Read/Write cycle times)

- High-speed access with tA = 3.8 ns

- Bus matching on both ports: ×80, ×40, ×20, ×10

- Free-running CLKA and CLKB. Clocks may be asynchronous or coincident