CY9DF126 Overview

Description

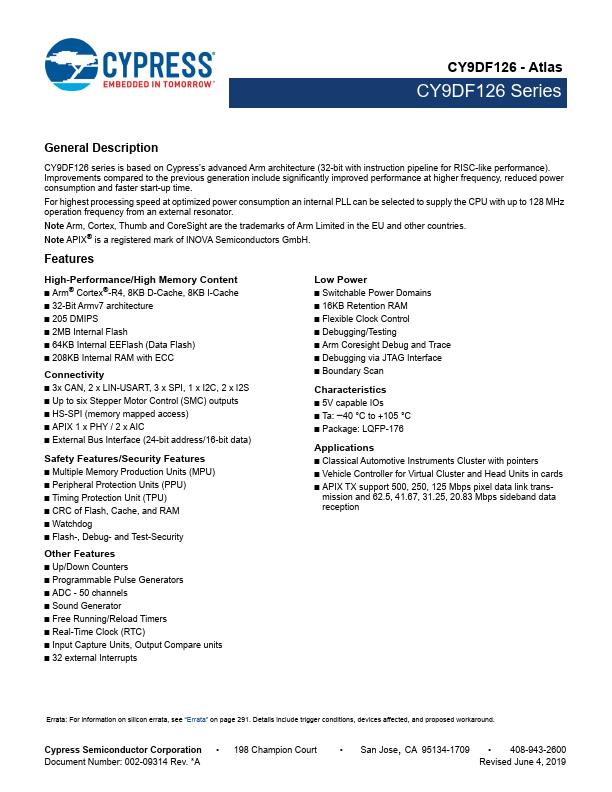

CY9DF126 series is based on Cypress’s advanced Arm architecture (32-bit with instruction pipeline for RISC-like performance). Improvements compared to the previous generation include significantly improved performance at higher frequency, reduced power consumption and faster start-up time.

Key Features

- Arm® Cortex®-R4, 8KB D-Cache, 8KB I-Cache

- 32-Bit Armv7 architecture

- 2MB Internal Flash

- 64KB Internal EEFlash (Data Flash)

- 208KB Internal RAM with ECC Connectivity

- 3x CAN, 2 x LIN-USART, 3 x SPI, 1 x I2C, 2 x I2S

- Up to six Stepper Motor Control (SMC) outputs

- HS-SPI (memory mapped access)

- APIX 1 x PHY / 2 x AIC

- External Bus Interface (24-bit address/16-bit data) Safety Features/Security Features