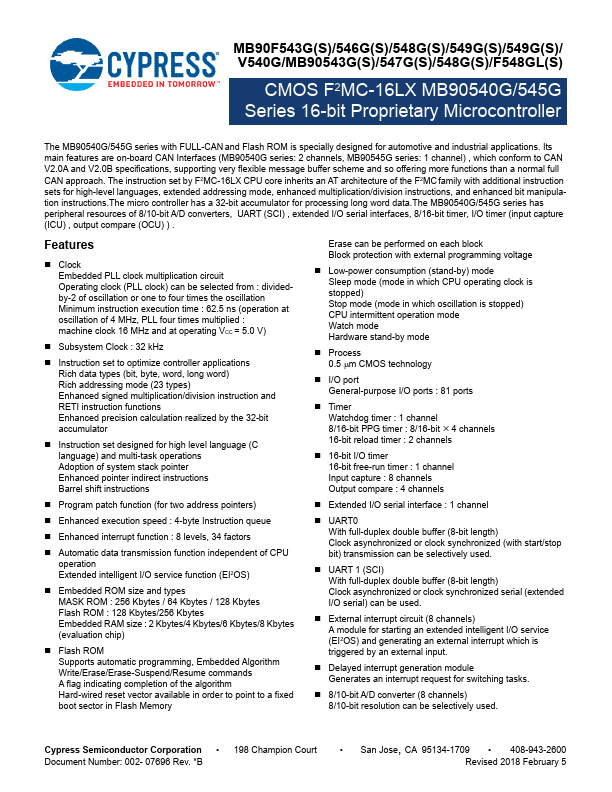

MB90F543G

Overview

- Clock Embedded PLL clock multiplication circuit Operating clock (PLL clock) can be selected from : dividedby-2 of oscillation or one to four times the oscillation Minimum instruction execution time : 62.5 ns (operation at oscillation of 4 MHz, PLL four times multiplied : machine clock 16 MHz and at operating VCC = 5.0 V)

- Subsystem Clock : 32 kHz

- Instruction set to optimize controller applications Rich data types (bit, byte, word, long word) Rich addressing mode (23 types) Enhanced signed multiplication/division instruction and RETI instruction functions Enhanced precision calculation realized by the 32-bit accumulator

- Instruction set designed for high level language (C language) and multi-task operations Adoption of system stack pointer Enhanced pointer indirect instructions Barrel shift instructions

- Program patch function (for two address pointers)

- Enhanced execu