PALCE20V8 Description

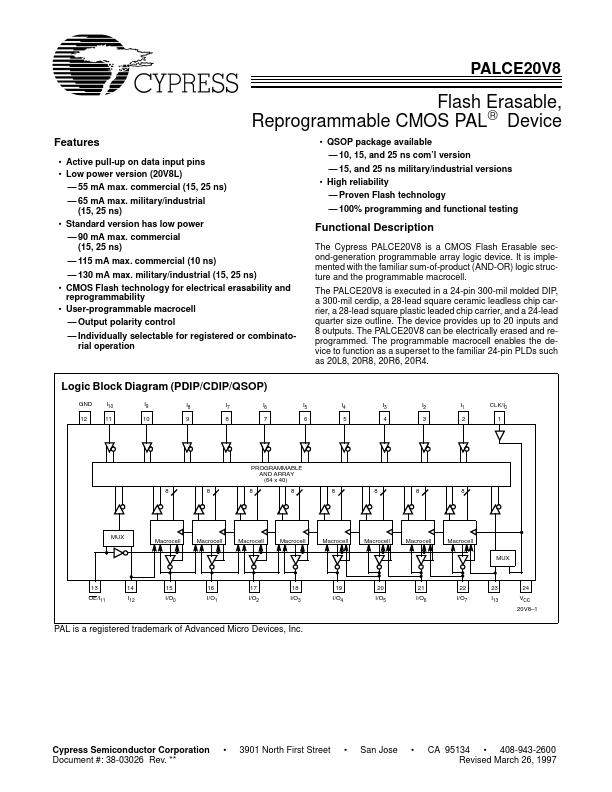

The Cypress PALCE20V8 is a CMOS Flash Erasable second-generation programmable array logic device. It is implemented with the familiar sum-of-product (AND-OR) logic structure and the programmable macrocell. The PALCE20V8 is executed in a 24-pin 300-mil molded DIP, a 300-mil cerdip, a 28-lead square ceramic leadless chip carrier, a 28-lead square plastic leaded chip carrier, and a 24-lead quarter size outline.

PALCE20V8 Key Features

- Active pull-up on data input pins

- Low power version (20V8L)

- 55 mA max. mercial (15, 25 ns)

- 65 mA max. military/industrial (15, 25 ns)

- Standard version has low power

- 90 mA max. mercial (15, 25 ns)

- 115 mA max. mercial (10 ns)

- 130 mA max. military/industrial (15, 25 ns)

- CMOS Flash technology for electrical erasability and reprogrammability

- User-programmable macrocell