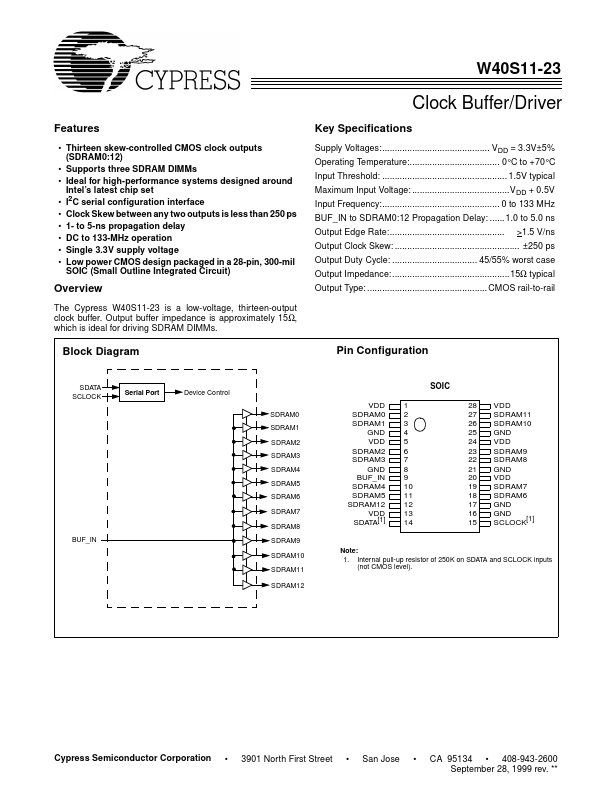

W40S11-23 Description

Provides buffered copy of BUF_IN. The propagation delay from a rising input edge to a rising output edge is 1 to 5 ns. All outputs are skew controlled to within ± 250 ps of each other.

W40S11-23 Key Features

- Thirteen skew-controlled CMOS clock outputs (SDRAM0:12)

- Supports three SDRAM DIMMs

- Ideal for high-performance systems designed around Intel’s latest chip set

- I2C serial configuration interface

- Clock Skew between any two outputs is less than 250 ps

- 1- to 5-ns propagation delay

- DC to 133-MHz operation

- Single 3.3V supply voltage

- Low power CMOS design packaged in a 28-pin, 300-mil SOIC (Small Outline Integrated Circuit)

- VDD = 3.3V±5% Operating Temperature