Datasheet Summary

Description

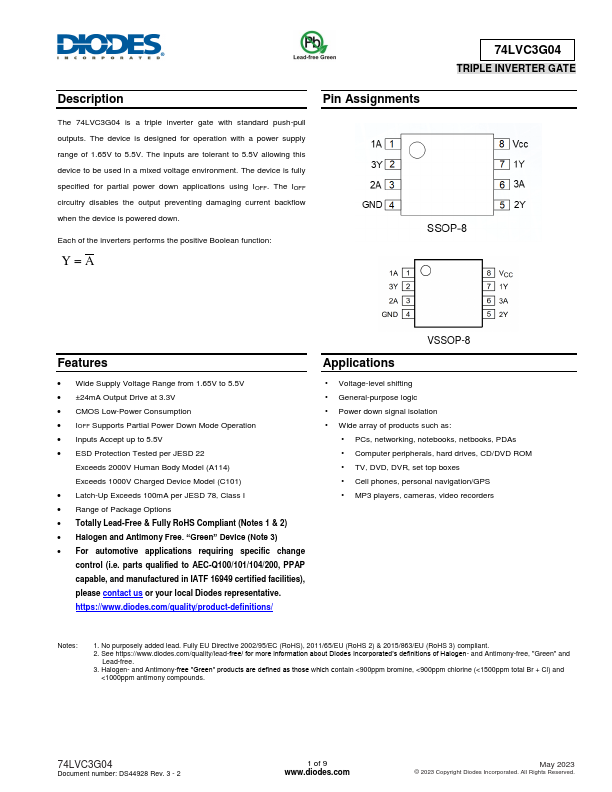

Pin Assignments

The 74LVC3G04 is a triple inverter gate with standard push-pull outputs. The device is designed for operation with a power supply range of 1.65V to 5.5V. The inputs are tolerant to 5.5V allowing this device to be used in a mixed voltage environment. The device is fully specified for partial power down applications using IOFF. The IOFF circuitry disables the output preventing damaging current backflow when the device is powered down.

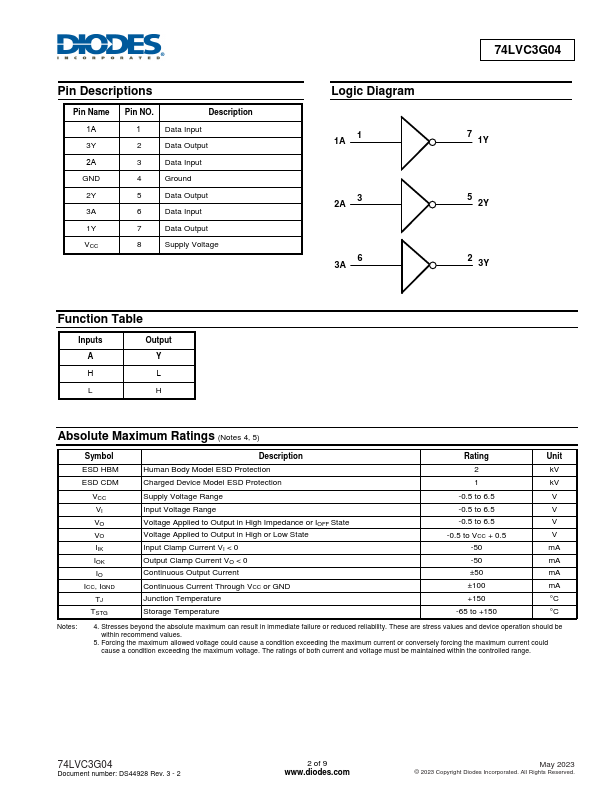

Each of the inverters performs the positive Boolean function:

YA

TRIPLE INVERTER GATE

Features

- Wide Supply Voltage Range from 1.65V to 5.5V

- ±24mA Output Drive at 3.3V

- CMOS Low-Power Consumption

- IOFF Supports...