DS12B887

DS12B887 is Real Time Clock manufactured by Dallas Semiconductor.

FEATURES

..

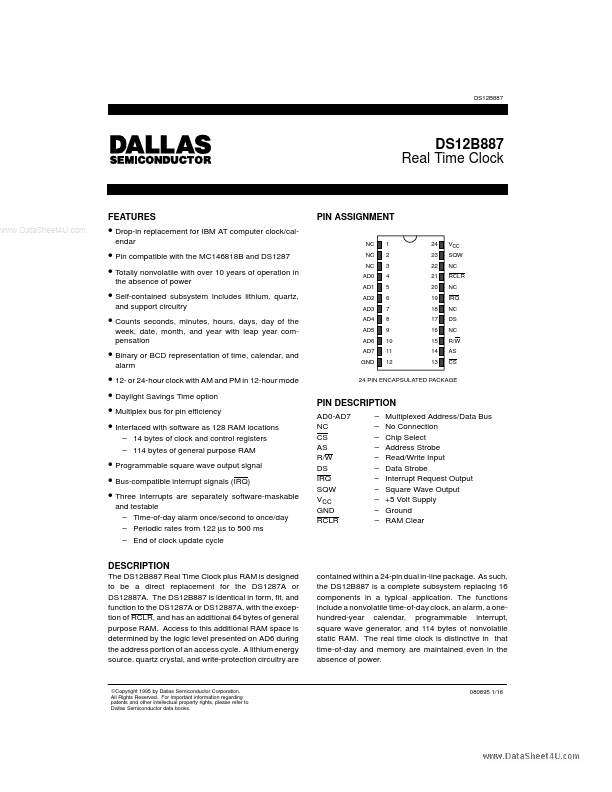

PIN ASSIGNMENT

NC NC NC AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 GND 1 2 3 4 5 6 7 8 9 10 11 12 24 23 22 21 20 19 18 17 16 15 14 13 VCC SQW NC RCLR NC IRQ NC DS NC R/W AS CS

- Drop-in replacement for IBM AT puter clock/calendar

- Pin patible with the MC146818B and DS1287

- Totally nonvolatile with over 10 years of operation in the absence of power

- Self-contained

- Counts subsystem includes lithium, quartz, and support circuitry seconds, minutes, hours, days, day of the week, date, month, and year with leap year pensation alarm

- Binary or BCD representation of time, calendar, and

- 12- or 24-hour clock with AM and PM in 12-hour mode

- Daylight Savings Time option

- Multiplex bus for pin efficiency

- Interfaced with software as 128 RAM locations

- 14 bytes of clock and control registers

- 114 bytes of general purpose RAM

24 PIN ENCAPSULATED PACKAGE

PIN DESCRIPTION

AD0-AD7 NC CS AS R/W DS IRQ SQW VCC GND RCLR

- -

- -

- -

- -

- -

- Multiplexed Address/Data Bus No Connection Chip Select Address Strobe Read/Write Input Data Strobe Interrupt Request Output Square Wave Output +5 Volt Supply Ground RAM Clear

- Programmable square wave output signal

- Bus-patible interrupt signals (IRQ)

- Three interrupts are separately software-maskable and testable

- Time-of-day alarm once/second to once/day

- Periodic rates from 122 µs to 500 ms

- End of clock update cycle

DESCRIPTION

The DS12B887 Real Time Clock plus RAM is designed to be a direct replacement for the DS1287A or DS12887A. The DS12B887 is identical in form, fit, and function to the DS1287A or DS12887A, with the exception of RCLR, and has an additional 64 bytes of general purpose RAM. Access to this additional RAM space is determined by the logic level presented on AD6 during the address portion of an access cycle. A lithium energy source, quartz crystal, and write-protection circuitry are contained within a 24-pin dual in-line package. As such, the DS12B887 is a plete subsystem replacing 16 ponents in a...