DP3ED32MX8RY5

DP3ED32MX8RY5 is 3.3V EDO DRAM manufactured by Dense-Pac Microsystems.

- Part of the DP3ED32MX8RY5-Dense comparator family.

- Part of the DP3ED32MX8RY5-Dense comparator family.

DESCRIPTION

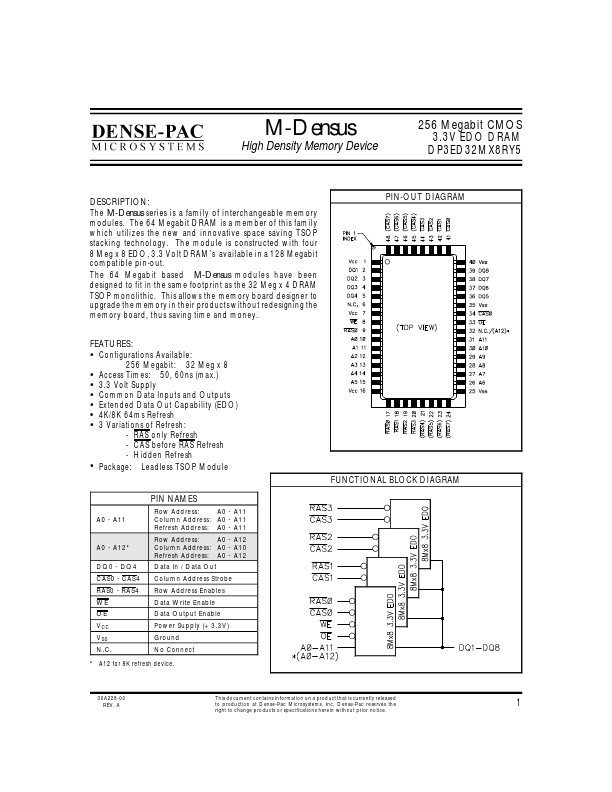

: The M-Densus series is a family of interchangeable memory modules. The 64 Megabit DRAM is a member of this family which utilizes the new and innovative space saving TSOP stacking technology. The module is constructed with four 8 Meg x 8 EDO, 3.3 Volt DRAM’s available in a 128 Megabit patible pin-out. The 64 Megabit based M-Densus modules have been designed to fit in the same footprint as the 32 Meg x 4 DRAM TSOP monolithic. This allows the memory board designer to upgrade the memory in their products without redesigning the memory board, thus saving time and money.

PIN-OUT DIAGRAM

FEATURES

:

- Configurations Available:

256 Megabit: 32 Meg x 8

- Access Times: 50, 60ns (max.)

- 3.3 Volt Supply

- mon Data Inputs and Outputs

- Extended Data Out Capability (EDO)

- 4K/8K 64ms Refresh

- 3 Variations of Refresh:

- RAS only Refresh

- CAS before RAS Refresh

- Hidden Refresh

- Package: Leadless TSOP Module

A0

- A11

A0

- A12-

DQ0

- DQ4 CAS0

- CAS4 RAS0

- RAS4 WE OE VCC VSS N.C.

PIN NAMES Row Address: A0

- A11 Column Address: A0

- A11 Refresh Address: A0

- A11 Row Address: A0

- A12 Column Address: A0

- A10 Refresh Address: A0

- A12 Data In / Data Out Column Address Strobe Row Address Enables Data Write Enable Data Output Enable Power Supply (+3.3V) Ground No Connect

- A12 for 8K refresh device.

FUNCTIONAL BLOCK DIAGRAM

30A228-00 REV. A

This document contains information on a product that is currently released to production at Dense-Pac Microsystems, Inc. Dense-Pac reserves the right to change products or specifications herein without prior notice.

DP3ED32MX8RY5 M-Densus

PRELIMINARY

ORDERING...