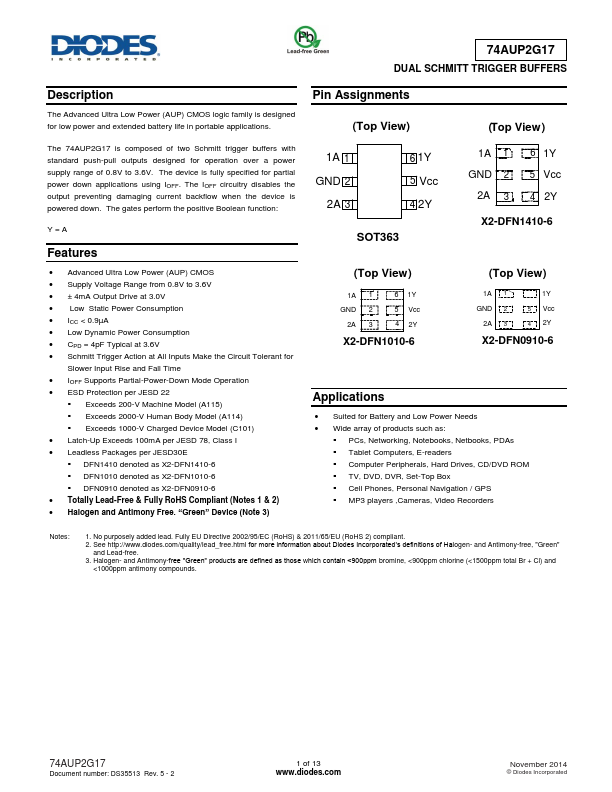

74AUP2G17

Overview

The Advanced Ultra Low Power (AUP) CMOS logic family is designed for low power and extended battery life in portable applications. The 74AUP2G17 is composed of two Schmitt trigger buffers with standard push-pull outputs designed for operation over a power supply range of 0.8V to 3.6V.

- Advanced Ultra Low Power (AUP) CMOS

- Supply Voltage Range from 0.8V to 3.6V

- ± 4mA Output Drive at 3.0V

- Low Static Power Consumption

- ICC < 0.9µA

- Low Dynamic Power Consumption

- CPD = 4pF Typical at 3.6V

- Schmitt Trigger Action at All Inputs Make the Circuit Tolerant for Slower Input Rise and Fall Time

- IOFF Supports Partial-Power-Down Mode Operation

- ESD Protection per JESD 22