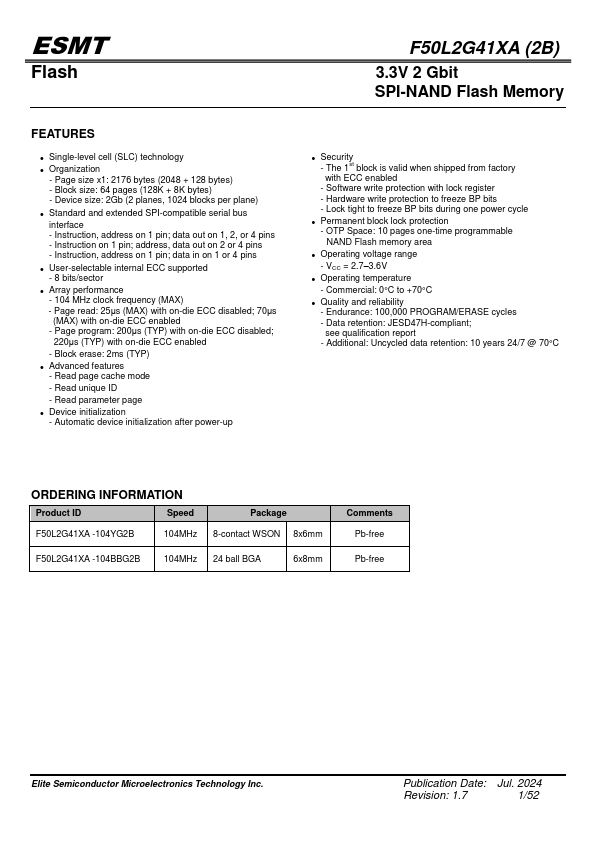

F50L2G41XA-104BBG2B Overview

Description

Serial peripheral interface (SPI) NAND is an SLC NAND Flash memory devic.

Key Features

- Single-level cell (SLC) technology

- Organization

- Page size x1: 2176 bytes (2048 + 128 bytes)

- Block size: 64 pages (128K + 8K bytes)

- Device size: 2Gb (2 planes, 1024 blocks per plane)