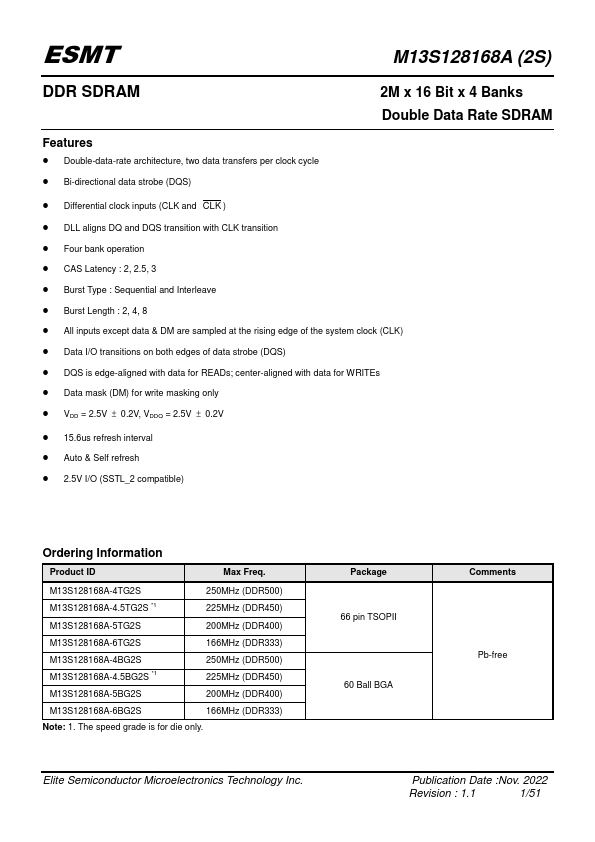

M13S128168A-4.5BG2S

Overview

- Double-data-rate architecture, two data transfers per clock cycle

- Bi-directional data strobe (DQS)

- Differential clock inputs (CLK and CLK )

- DLL aligns DQ and DQS transition with CLK transition

- Four bank operation

- CAS Latency : 2, 2.5, 3

- Burst Type : Sequential and Interleave

- Burst Length : 2, 4, 8

- All inputs except data & DM are sampled at the rising edge of the system clock (CLK)

- Data I/O transitions on both edges of data strobe (DQS)