M14D1G8128A-1.8BG2P Description

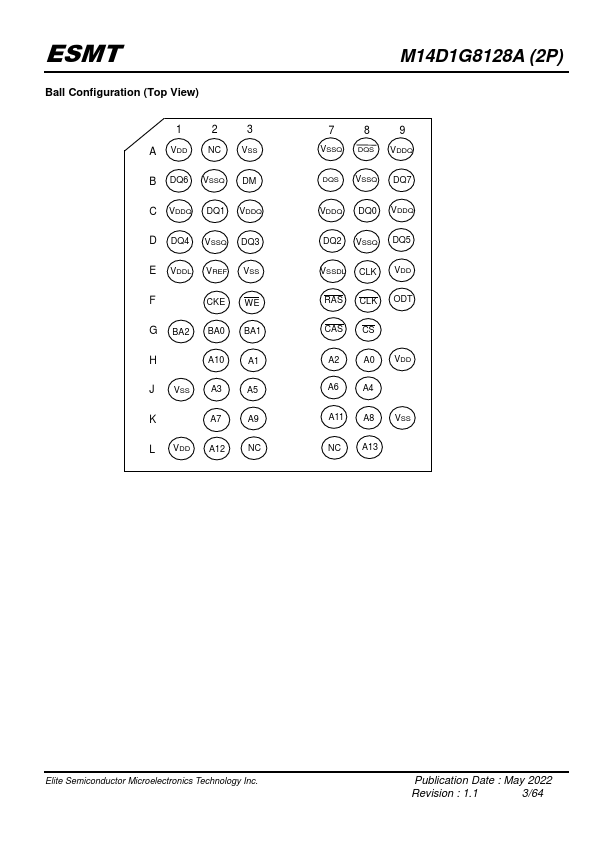

Pin Name A0~A13, BA0~BA2 DQ0~DQ7 RAS CAS WE VSS VDD DQS, DQS ODT NC Function Address inputs - Row address A0~A13 - Column address A0~A9 A10/AP : Auto.

M14D1G8128A-1.8BG2P Key Features

- JEDEC Standard

- VDD = 1.8V ± 0.1V, VDDQ = 1.8V ± 0.1V

- Internal pipelined double-data-rate architecture; two data access per clock cycle

- Bi-directional differential data strobe (DQS, DQS ); DQS can be disabled for single-ended data strobe operation

- On-chip DLL

- Differential clock inputs (CLK and CLK )

- DLL aligns DQ and DQS transition with CLK transition

- 8 bank operation

- CAS Latency : 3, 4, 5, 6, 7

- Additive Latency: 0, 1, 2, 3, 4, 5, 6