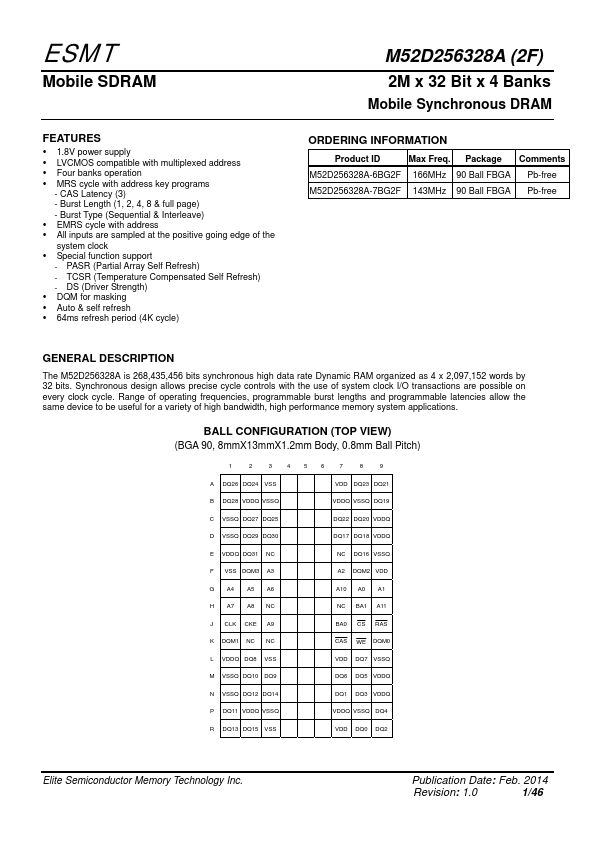

M52D256328A-6BG2F

Description

The M52D256328A is 268,435,456 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 32 bits. Synchronous design allows precise cycle controls with the use of system clock I/O transactions are possible on every clock cycle.

Key Features

- CAS Latency (3)

- Burst Length (1, 2, 4, 8 & full page)

- PASR (Partial Array Self Refresh)