| Part | M53D5123216A-7.5BG |

|---|---|

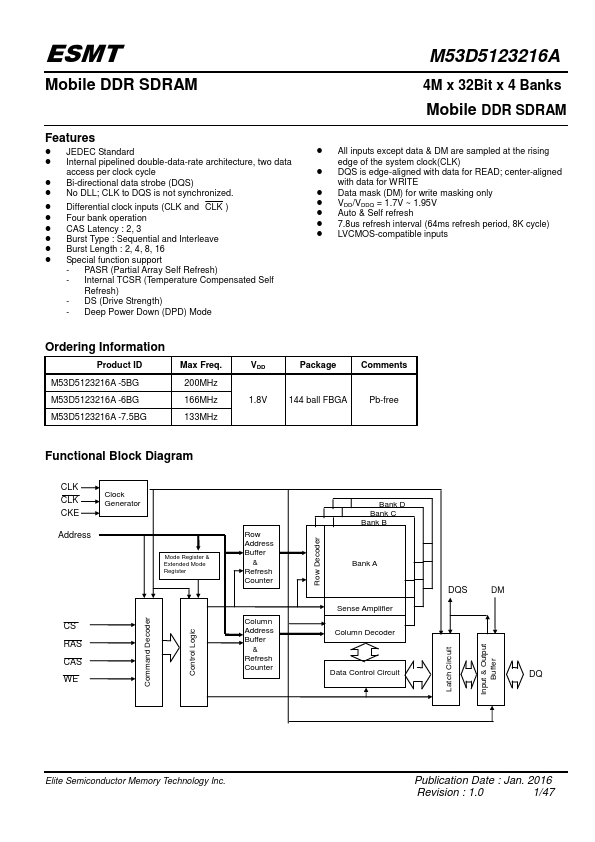

| Description | 4M x 32Bit x 4 Banks Mobile DDR SDRAM |

| Manufacturer | Elite Semiconductor Microelectronics Technology |

| Size | 1.26 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CXDB4ABAM-MK | CXMT | LPDDR4X SDRAM |

| CXDB5CCAM-MK | CXMT | LPDDR4X SDRAM |

| CXDB5CBAM-MA-B | CXMT | 4GB LPDDR4X SDRAM |