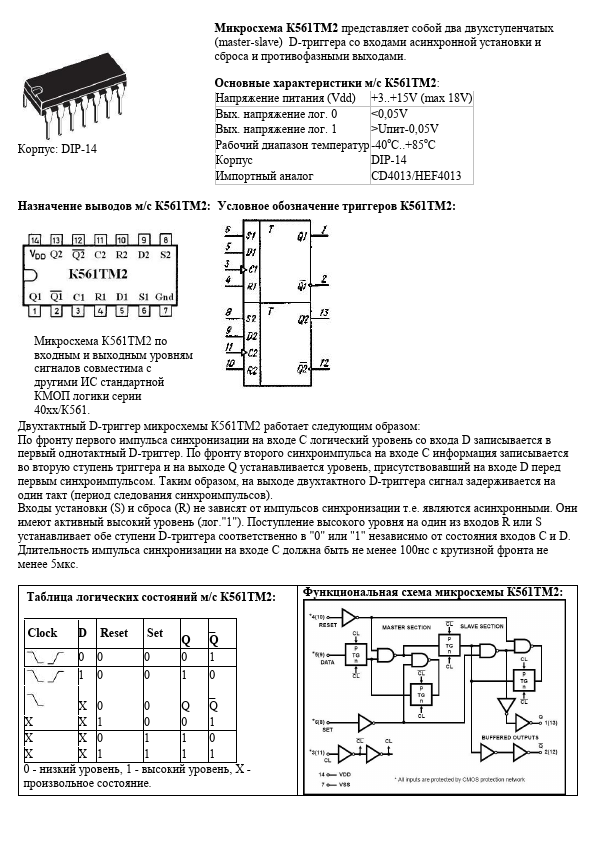

| Part | K561TM2 |

|---|---|

| Description | 2-stage (Master-slave) D flip-flop |

| Manufacturer | Unknown Manufacturer |

| Size | 206.19 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| K5610 | Kodenshi AUK Group | Photocoupler(These Photocouplers consist of a Gallium Arsenide Infrared Emitting) |

| K5611 | Kodenshi AUK Group | Photocoupler(These Photocouplers consist of a Gallium Arsenide Infrared Emitting) |

| K561 | Knox Semiconductor Inc | LOW LEVEL ZENER DIODES SHARP KNEE/ LOW IMPEDANCE |

| K561 | Aeroflex | Silicon Zener Diodes |