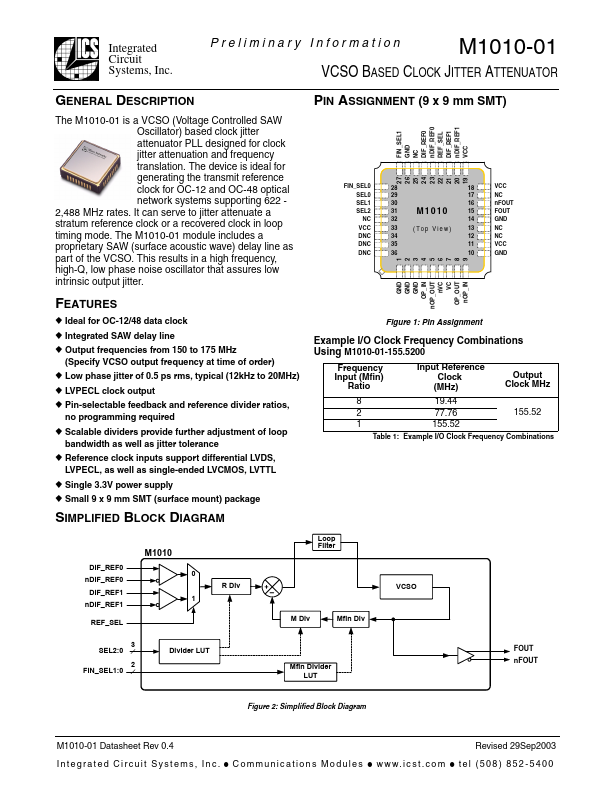

M1010-01 Key Features

- Ideal for OC-12/48 data clock

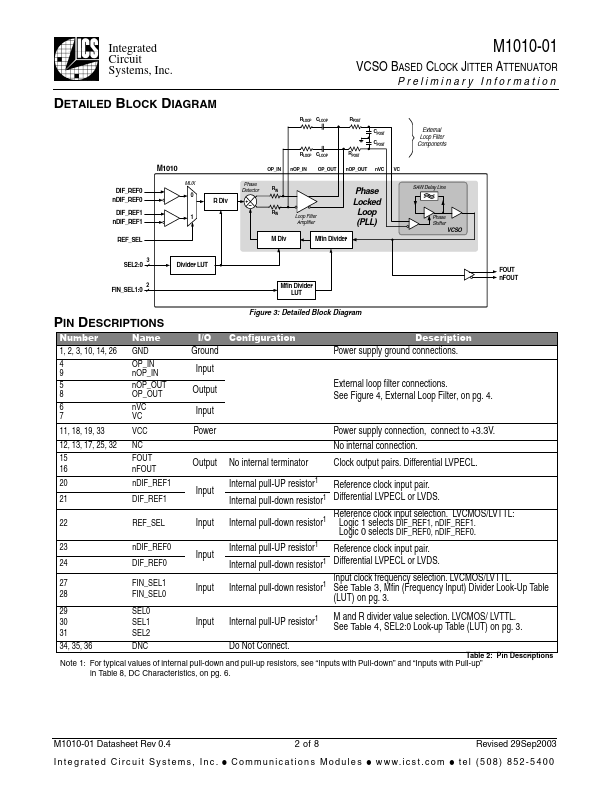

- Integrated SAW delay line

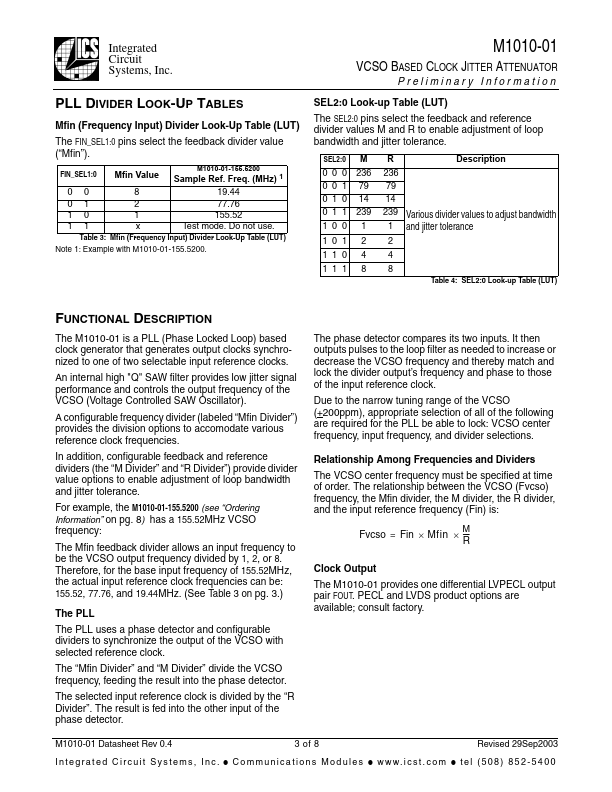

- Output frequencies from 150 to 175 MHz (Specify VCSO output frequency at time of order)

- Low phase jitter of 0.5 ps rms, typical (12kHz to 20MHz)

- LVPECL clock output

- Pin-selectable feedback and reference divider ratios, no programming required

- Scalable dividers provide further adjustment of loop bandwidth as well as jitter tolerance

- Reference clock inputs support differential LVDS, LVPECL, as well as single-ended LVCMOS, LVTTL

- Single 3.3V power supply

- Small 9 x 9 mm SMT (surface mount) package