PLL500-17 Overview

Description

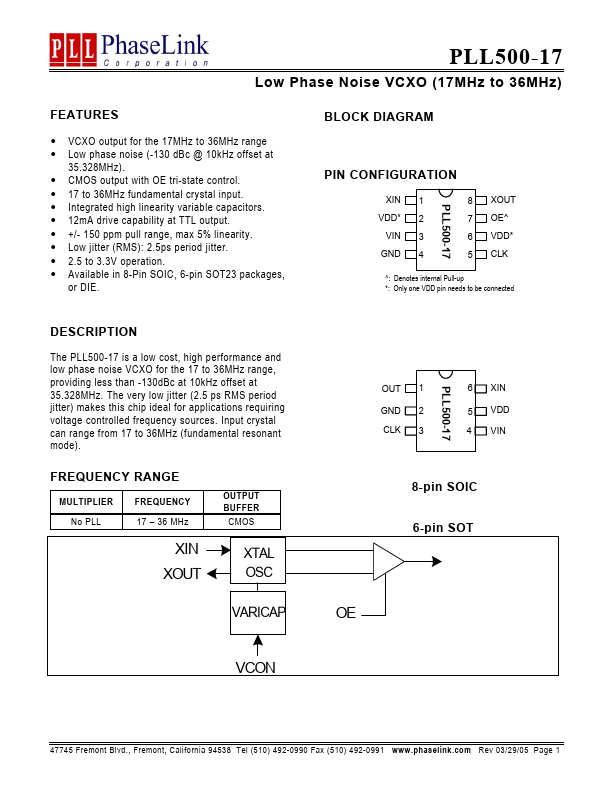

The PLL500-17 is a low cost, high performance and low phase noise VCXO for the 17 to 36MHz range, providing less than -130dBc at 10kHz offset at 35.328MHz. The very low jitter (2.5 ps RMS period jitter) makes this chip ideal for applications requiring voltage controlled frequency sources.

Key Features

- VCXO output for the 17MHz to 36MHz range Low phase noise (-130 dBc @ 10kHz offset at 35.328MHz)

- CMOS output with OE tri-state control

- 17 to 36MHz fundamental crystal input

- Integrated high linearity variable capacitors

- 12mA drive capability at TTL output