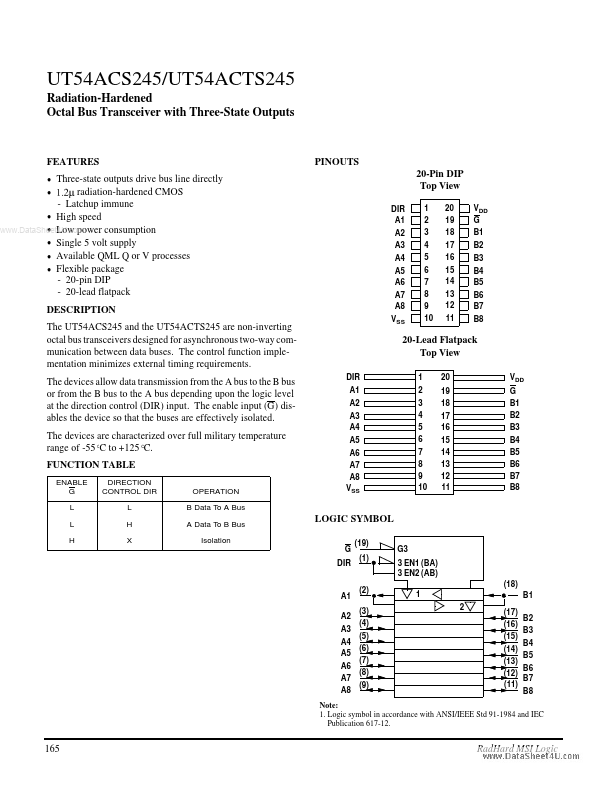

- Part: UT54ACTS245

- Description: Ocral Bus Transceiver

- Manufacturer: Unknown Manufacturer

- Size: 68.95 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| UT54ACTS240 | Aeroflex Circuit Technology | Octal Buffers & Line Drivers |

| UT54ACTS244 | Aeroflex Circuit Technology | Octal Buffers & Line Drivers |