UT62256C

UT62256C is 32K X 8 BIT LOW POWER CMOS SRAM manufactured by Unknown Manufacturer.

DESCRIPTION

The UT62256C is a 262,144-bit low power CMOS static random access memory organized as 32,768 words by 8 bits. It is fabricated using high performance, high reliability CMOS technology. The UT62256C is designed for high-speed and low power application. It is particularly well suited for battery back-up nonvolatile memory application. The UT62256C operates from a single 5V power supply and all inputs and outputs are fully TTL patible

FEATURES

Access time : 35/70ns (max.) Low power consumption: Operating : 40/30 m A (typical.) Standby : 3m A (typical) normal 2u A (typical) L-version 1u A (typical) LL-version Single 5V power supply All inputs and outputs are TTL patible Fully static operation Three state outputs Data retention voltage : 2V (min.) Package : 28-pin 600 mil PDIP 28-pin 330 mil SOP 28-pin 8mmx13.4mm STSOP

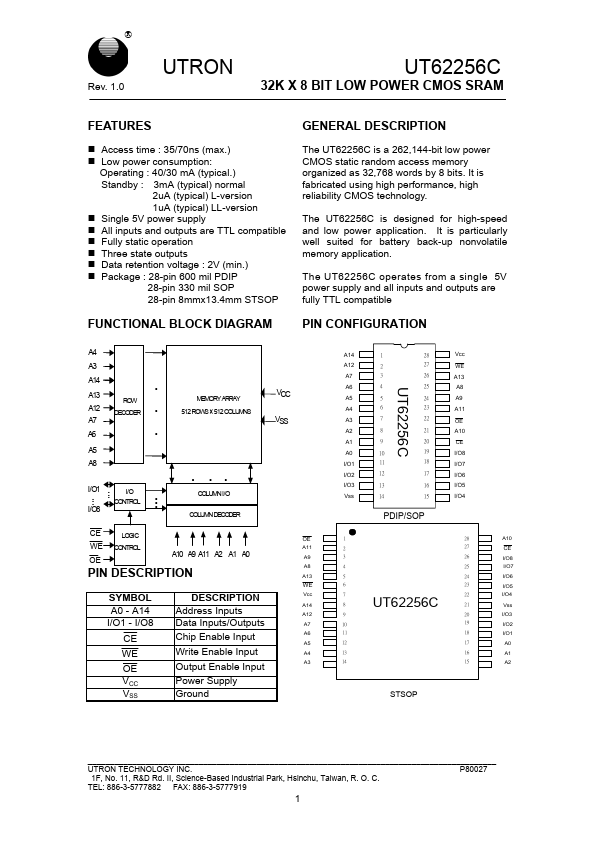

FUNCTIONAL BLOCK DIAGRAM

A4 A3 A14 A13 A12 A7 A6 A5 A8

ROW DECODER

PIN CONFIGURATION

A14 A12 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vcc

. . .

MEMORY ARRAY 512 ROW S × 512 COLUMNS

A7

A13 A8 A9 A11

VCC VSS

A6 A5 A4 A3 A2 A1 A0 I/O1

A10

I/O8 I/O7 I/O6 I/O5 I/O4

.

I/O1 . . I/O8

. .

COLUMN I/O

I/O2 I/O3 Vss

. . .

.

I/O CONTROL

. . .

COLUMN DECODER LOGIC CONTROL

PDIP/SOP

1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 A10

CE WE OE

A10 A9 A11 A2 A1 A0

A11 A9 A8 A13

I/O8 I/O7 I/O6 I/O5 I/O4 Vss I/O3 I/O2 I/O1 A0 A1 A2

PIN DESCRIPTION

SYMBOL...