N2DS12H16CT

N2DS12H16CT is 128Mb DDR SDRAM manufactured by Elixir.

128Mb DDR SDRAM Features

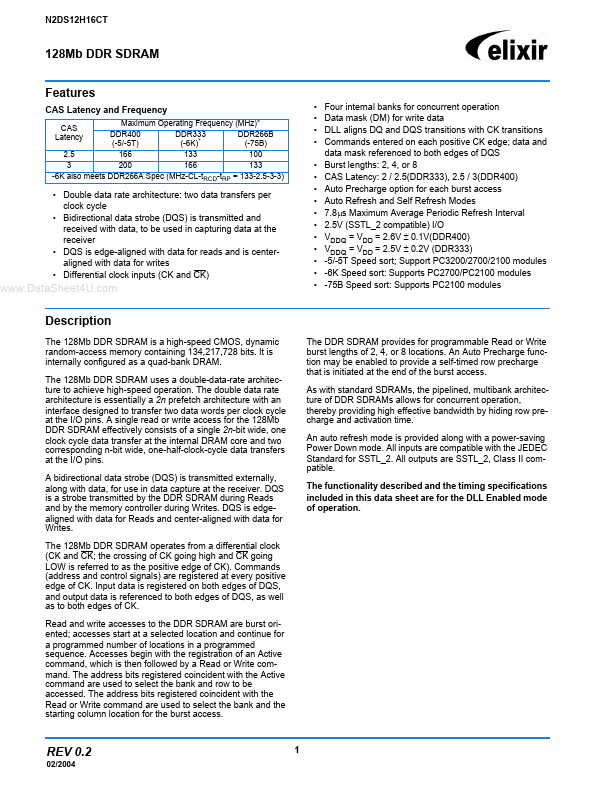

CAS Latency and Frequency

Maximum Operating Frequency (MHz)- DDR400 DDR333 DDR266B (-5/-5T) (-6K)- (-75B) 2.5 166 133 100 3 200 166 133

- -6K also meets DDR266A Spec (MHz-CL-t RCD-tRP = 133-2.5-3-3) CAS Latency

- -

- -

- -

- -

- -

- -

- -

- - Double data rate architecture: two data transfers per clock cycle

- Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver

- DQS is edge-aligned with data for reads and is centeraligned with data for writes

- Differential clock inputs (CK and CK)

..

Four internal banks for concurrent operation Data mask (DM) for write data DLL aligns...