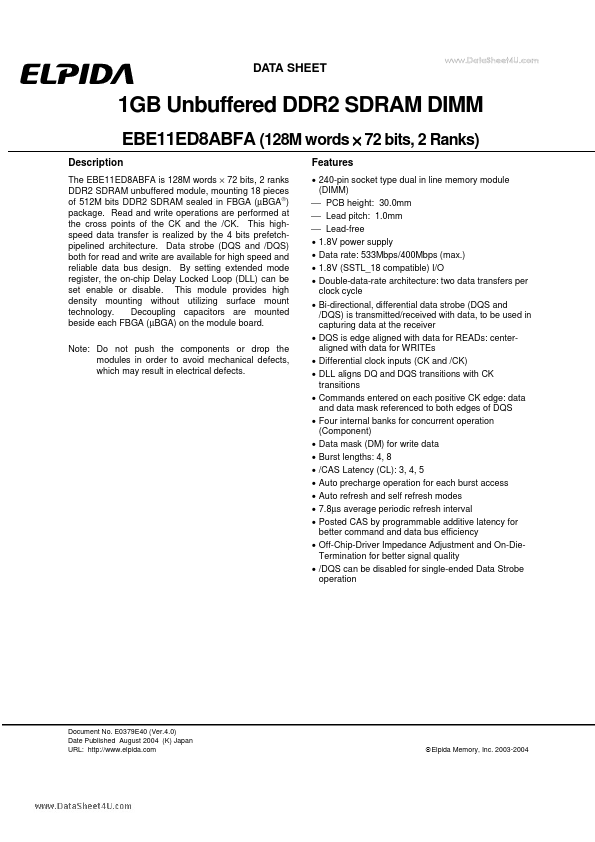

EBE11ED8ABFA

Description

The EBE11ED8ABFA is 128M words × 72 bits, 2 ranks DDR2 SDRAM unbuffered module, mounting 18 pieces of 512M bits DDR2 SDRAM sealed in FBGA (µBGA) package. Read and write operations are performed at the cross points of the CK and the /CK.

Key Features

- 240-pin socket type dual in line memory module (DIMM) PCB height: 30.0mm Lead pitch: 1.0mm Lead-free

- 1.8V power supply

- Data rate: 533Mbps/400Mbps (max.)

- 1.8V (SSTL_18 compatible) I/O

- Double-data-rate architecture: two data transfers per clock cycle

- Bi-directional, differential data strobe (DQS and /DQS) is transmitted/received with data, to be used in capturing data at the receiver

- DQS is edge aligned with data for READs: centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge: data and data mask referenced to both edges of DQS