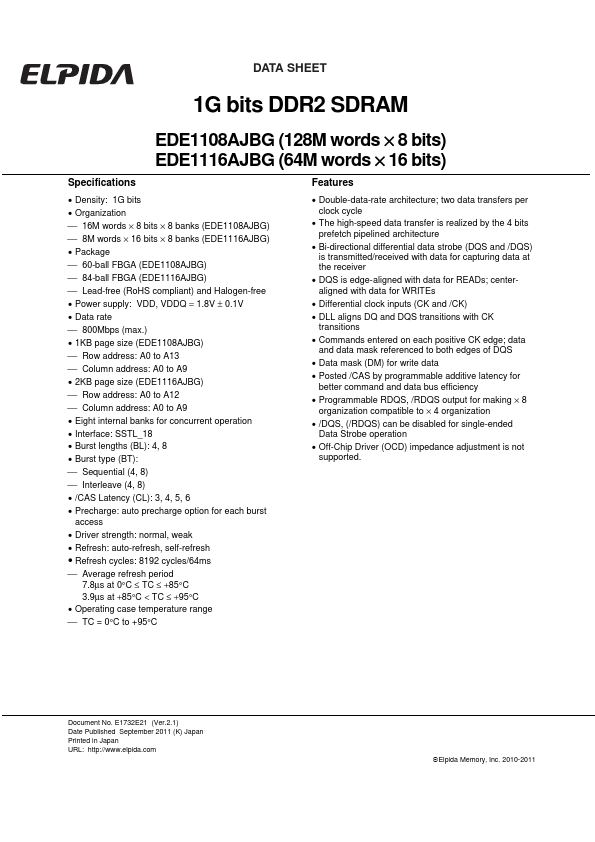

EDE1116AJBG

Features

- Double-data-rate architecture; two data transfers per clock cycle

- The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

- DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

- Posted /CAS by programmable additive latency for better mand and data bus efficiency

- Programmable RDQS, /RDQS output for making × 8 organization patible to × 4 organization

- /DQS, (/RDQS) can be disabled for single-ended Data Strobe operation

- Off-Chip Driver (OCD) impedance adjustment is not supported.

- Refresh cycles: 8192 cycles/64ms

Average refresh period 7.8µs at 0°C ≤ TC ≤ +85°C 3.9µs at...