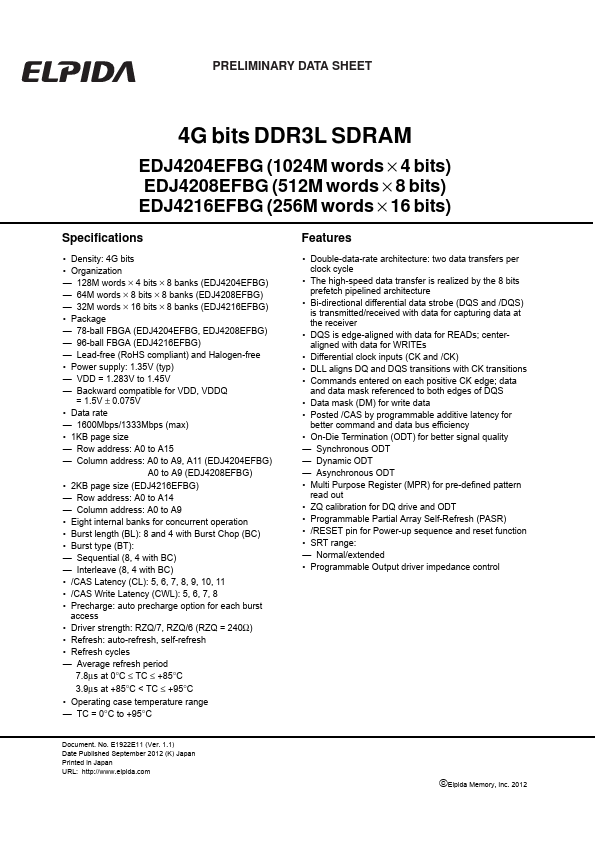

EDJ4216EFBG Description

1.35V (typ) VDD = 1.283V to 1.45V Backward patible for VDD, VDDQ = 1.5V ± 0.075V Data rate 1600Mbps/1333Mbps (max) 1KB page size Row address: A0 to A15 Column address: A0 to A14 Column address:.

EDJ4216EFBG Key Features

- Double-data-rate architecture: two data transfers per clock cycle

- The high-speed data transfer is realized by the 8 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the recei

- DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data

- Data mask (DM) for write data

- On-Die Termination (ODT) for better signal quality

- Synchronous ODT