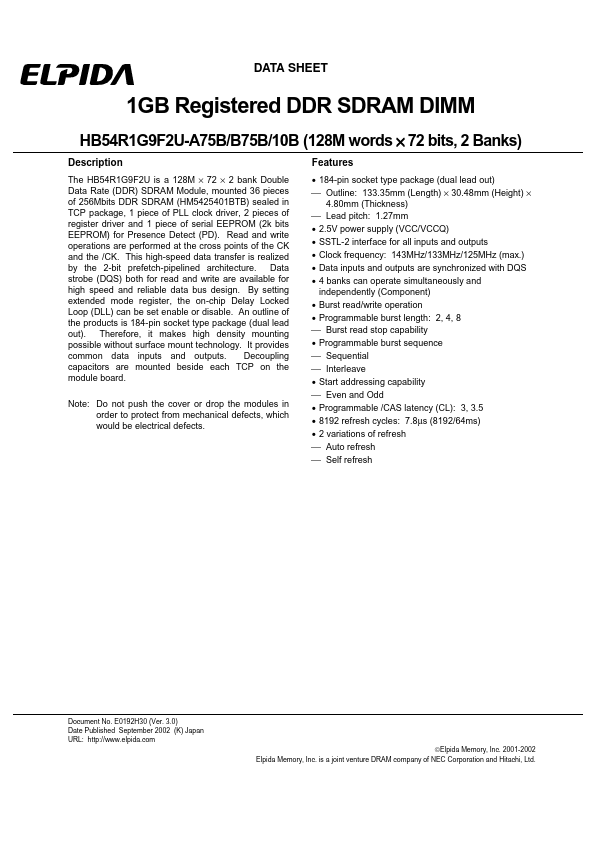

HB54R1G9F2U-10B

Overview

The HB54R1G9F2U is a 128M × 72 × 2 bank Double Data Rate (DDR) SDRAM Module, mounted 36 pieces of 256Mbits DDR SDRAM (HM5425401BTB) sealed in TCP package, 1 piece of PLL clock driver, 2 pieces of register driver and 1 piece of serial EEPROM (2k bits EEPROM) for Presence Detect (PD). Read and write operations are performed at the cross points of the CK and the /CK.

- 184-pin socket type package (dual lead out) Outline: 133.35mm (Length) × 30.48mm (Height) × 4.80mm (Thickness) Lead pitch: 1.27mm

- 2.5V power supply (VCC/VCCQ)

- SSTL-2 interface for all inputs and outputs

- Clock frequency: 143MHz/133MHz/125MHz (max.)

- Data inputs and outputs are synchronized with DQS

- 4 banks can operate simultaneously and independently (Component)

- Burst read/write operation

- Programmable burst length: 2, 4, 8 Burst read stop capability

- Programmable burst sequence Sequential Interleave

- Start addressing capability Even and Odd