HM5425401B Description

The HM5425161B, the HM5425801B and the HM5425401B are the Double Data Rate (DDR) SDRAM devices. Read and write operations are performed at the cross points of the CLK and the CLK. This high speed data transfer is realized by the 2-bit prefetch piplined architecture.

HM5425401B Key Features

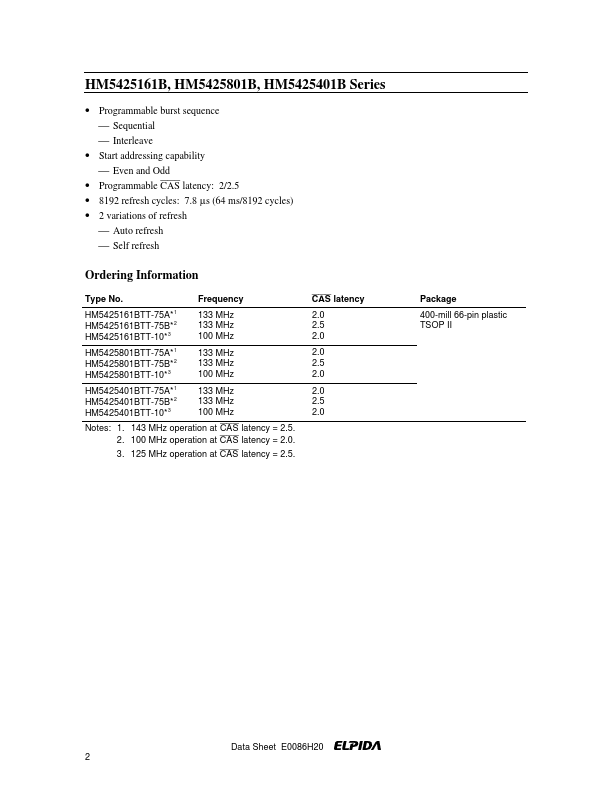

- Programmable burst sequence Sequential Interleave

- Start addressing capability Even and Odd

- Programmable CAS latency: 2/2.5

- 8192 refresh cycles: 7.8 µs (64 ms/8192 cycles)

- 2 variations of refresh Auto refresh Self refresh