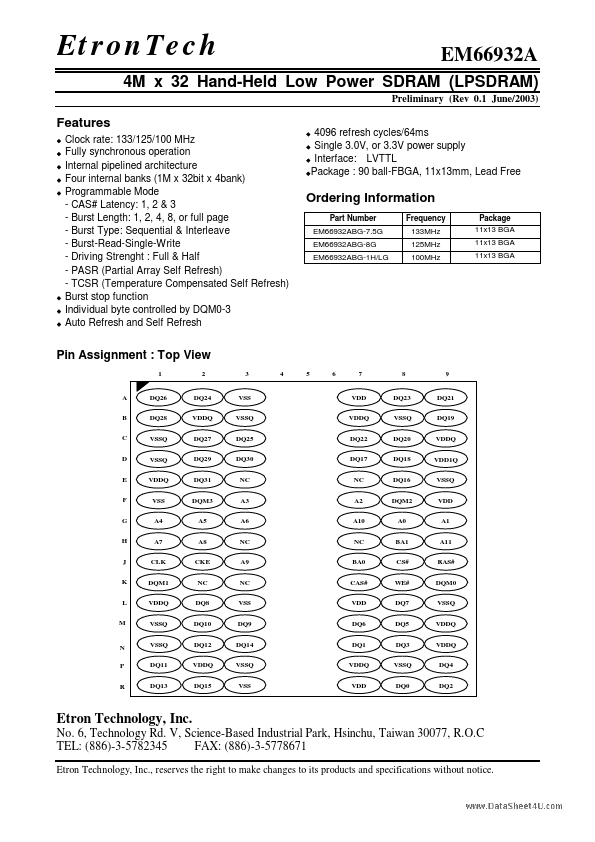

| Part | EM66932A |

|---|---|

| Description | 4M x 32 Hand-Held Low Power SDRAM |

| Manufacturer | Etron Technology |

| Size | 198.84 KB |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| CXDB4ABAM-MK | CXMT | LPDDR4X SDRAM |

| CXDB5CCAM-MK | CXMT | LPDDR4X SDRAM |

| CXDB5CBAM-MA-B | CXMT | 4GB LPDDR4X SDRAM |