EP504 Overview

Key Specifications

Package: Aluminum

Mount Type: Panel

Description

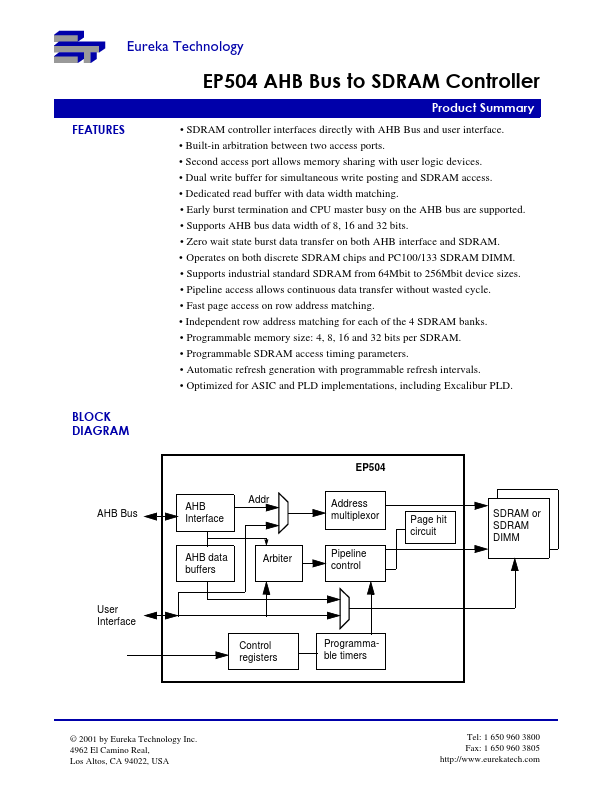

The AHB bus SDRAM controller provides high speed SDRAM for the system. It features two access ports.

Key Features

- SDRAM controller interfaces directly with AHB Bus and user interface

- Built-in arbitration between two access ports

- Second access port allows memory sharing with user logic devices

- Dual write buffer for simultaneous write posting and SDRAM access

- Dedicated read buffer with data width matching