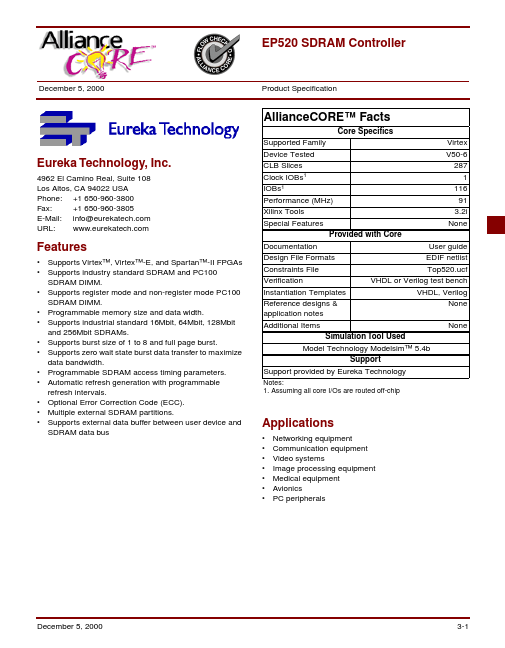

EP520 Overview

Key Specifications

Description

The EP520 SDRAM controller interfaces between a processor or DMA device with an SDRAM. It performs SDRAM read and write access based on process.

Key Features

- Supports Virtex™, Virtex™-E, and Spartan™-II FPGAs Supports industry standard SDRAM and PC100 SDRAM DIMM

- Supports register mode and non-register mode PC100 SDRAM DIMM

- Programmable memory size and data width

- Supports industrial standard 16Mbit, 64Mbit, 128Mbit and 256Mbit SDRAMs

- Supports burst size of 1 to 8 and full page burst