ST16C650A Overview

Key Specifications

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 2.97 V

Max Frequency: 50 MHz

Description

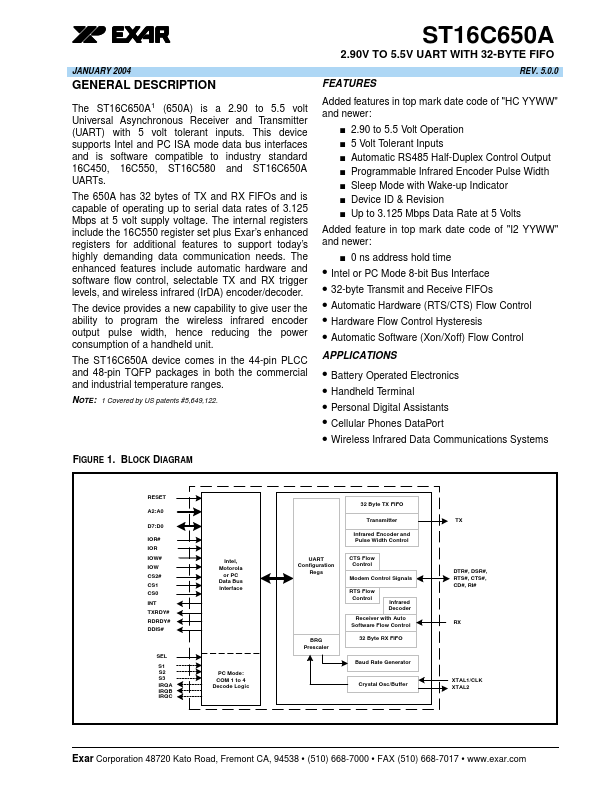

The ST16C650A1 (650A) is a 2.90 to 5.5 volt Universal Asynchronous Receiver and Transmitter (UART) with 5 volt tolerant inputs. This device supports Intel and PC ISA mode data bus interfaces and is software compatible to industry standard 16C450, 16C550, ST16C580 and ST16C650A UARTs.

Key Features

- Intel or PC Mode 8-bit Bus Interface

- 32-byte Transmit and Receive FIFOs

- Automatic Hardware (RTS/CTS) Flow Control

- Hardware Flow Control Hysteresis

- Automatic Software (Xon/Xoff) Flow Control