XRT71D00

Overview

The XRT71D00 is a single channel, single chip Jitter Attenuator, that meets the Jitter requirements specified in the ETSI TBR-24, Bellcore GR-499 and GR253 standards. In addition, the XRT71D00 also meets the Jitter and Wander specifications described in the ANSI T1.105.03b 1997, Bellcore GR-253 and GR-499 standards for Desynchronizing and Pointer adjustments in the DS3 to STS-SPE mapping applications.

- Meets the E3/DS3/STS-1 jitter requirements

- No external components required

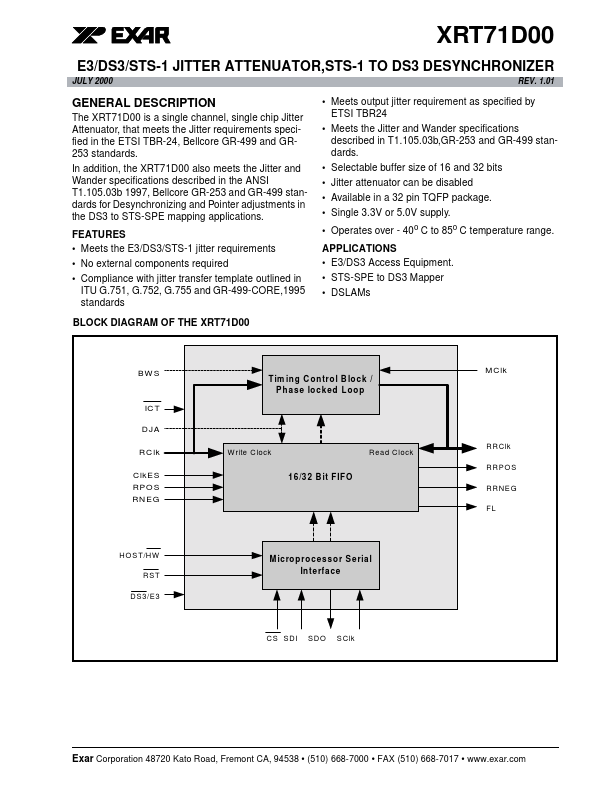

- Compliance with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE,1995 standards BLOCK DIAGRAM OF THE XRT71D00

- Meets output jitter requirement as specified by ETSI TBR24

- Meets the Jitter and Wander specifications described in T1.105.03b,GR-253 and GR-499 standards.

- Selectable buffer size of 16 and 32 bits

- Jitter attenuator can be disabled

- Available in a 32 pin TQFP package.

- Single 3.3V or 5.0V supply.

- Operates over - 400 C to 850 C temperature range. APPLICATIONS