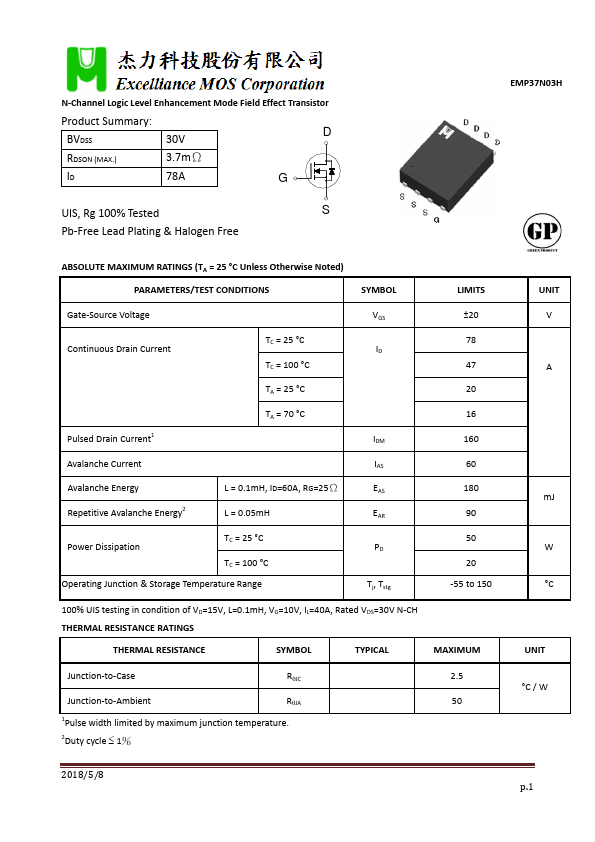

| Part | EMP37N03H |

|---|---|

| Description | N-Channel Logic Level Enhancement Mode Field Effect Transistor |

| Category | Transistor |

| Manufacturer | Excelliance MOS |

| Size | 269.54 KB |

Pricing from 0.0425 USD, available from UnikeyIC and Unikeyic (ICkey).

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| UnikeyIC | 30000 | 5000+ : 0.0425 USD 10000+ : 0.0418 USD 15000+ : 0.0407 USD |

View Offer |

| Unikeyic (ICkey) | 30000 | 5000+ : 0.0425 USD 10000+ : 0.0418 USD 15000+ : 0.0407 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| BDT88 | Inchange Semiconductor | Silicon PNP Power Transistor |

| KD333 | Tesla Elektronicke | Transistor |

| C828 | SEMTECH | NPN Silicon Transistor |