Datasheet Summary

FMD8C16LAx- 25Ex

512M(32Mx16) Low Power DDR SDRAM

Rev. 0.2, Jul. ‘12

Revision 0.2 Jul. 2012

Document Title

512M(32Mx16) Low Power DDR SDRAM

Revision History

Revision No.

History

0.0 Initial Draft 0.1 Adjusted DC parameters(IDD0, IDD4R, IDD4W, IDD6) 0.2 Changed tWTR (1CLK Æ 2CLKs)

FMD8C16LAx- 25Ex

Draft date

Dec. 15th, 2011 Jun. 28th, 2012 Jul. 27th, 2012

Remark

Preliminary

Rev. 0.2, Jul. ‘12

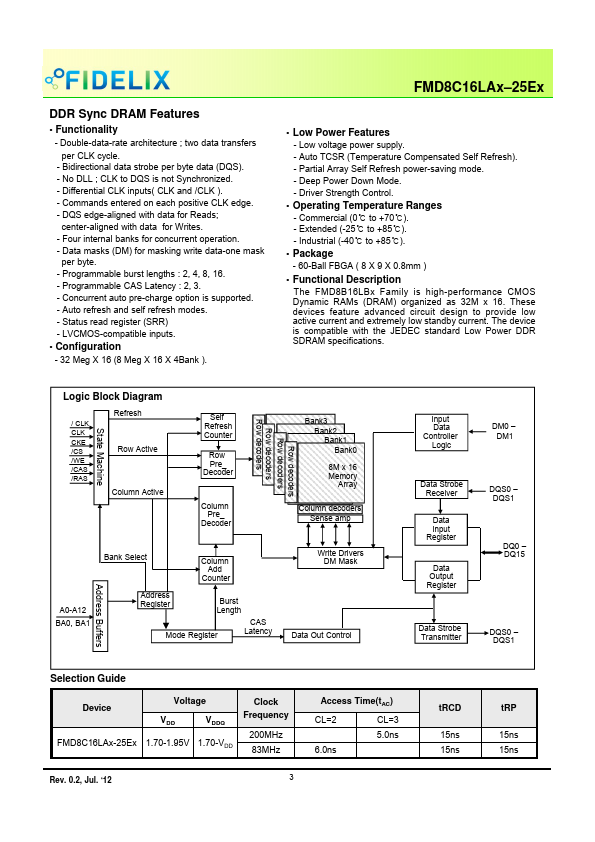

DDR Sync DRAM Features

- Functionality

- Double-data-rate architecture ; two data transfers per CLK cycle.

- Bidirectional data strobe per byte data (DQS).

- No DLL ; CLK to DQS is not Synchronized.

- Differential CLK inputs( CLK and /CLK ).

- mands entered on each positive CLK edge....