Description

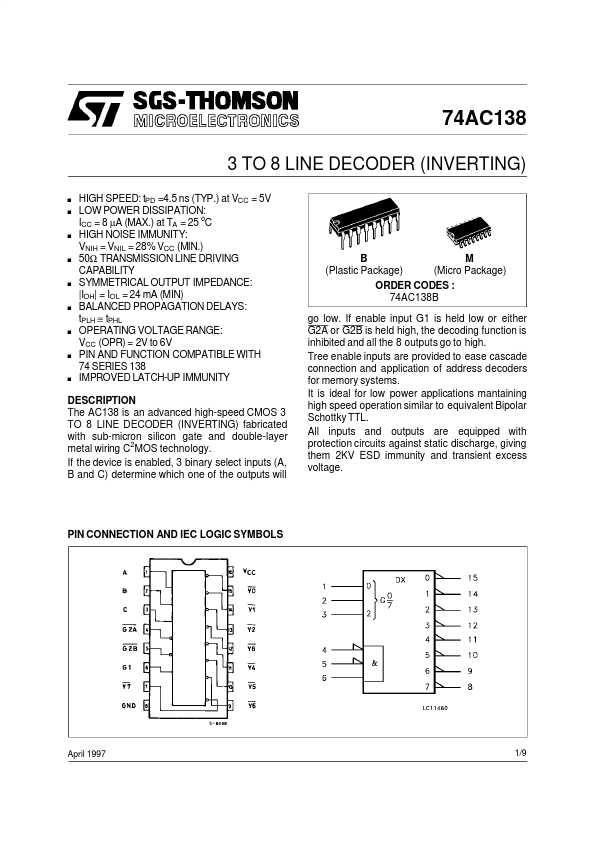

The AC138 is an advanced high-speed CMOS 3 TO 8 LINE DECODER (INVERTING) fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology. If the device is enabled, 3 binary select inputs (A, B and C) determine which one of the outputs will PIN CONNECTION AND IEC LOGIC SYMBOLS April 1997 1/9 74AC138 INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION PIN No 1, 2, 3 4, 5 6 15, 14, 13, 12, 11, 10, 9, 7 8 16 SYMBOL A, B, C G2A, G2B G1 Y0 to Y7 NAME AND F UNCTIO N Address Inputs Enable Inputs Enable Input Outputs GND VCC Ground (0V) Positive Supply Voltage TRUTH TABLE INPUTS ENABL E G 2B G2A G1 C X X L X X H X X H X X X L L H L L L H L L L H L L L H L L L H H L L H H L L H H L L H H X: Don’t Care OUTPUTS SEL ECT B X X X L L H H L L H H A X X X L H L H L H L H Y0 H H H L H H H H H H H Y1 H H H H L H H H H H H Y2 H H H H H L H H H H H Y3 H H H H H H L H H H H Y4 H H H H H H H L H H H Y5 H H H H H H H H L H H Y6 H H H H H H H H H L H Y7 H H H H H H H H H H L LOGIC DIAGRAM This logic diagram has not be used to estimate propagation delays 2/9 74AC138 Symbol VCC VI VO IIK IOK IO Tstg TL Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Current Storage Temperature Lead Temperature (10 sec) Parameter Value -0.5 to +7 -0.5 to VCC + 0.5 -0.5 to VCC + 0.5 ± 20 ± 20 ± 50 ± 400 -65 to +150 300 Unit V V V mA mA mA mA o o ICC or IGND DC VCC or Ground Current C C REMENDED OPERATING CONDITIONS Symbol VCC VI VO Top dt/dv Supply Voltage Input Voltage Output Voltage Operating Temperature: Input Rise and Fall Time VCC = 3.0, 4.5 or 5.5 V(note 1) Parameter Value 2 to 6 0 to VCC 0 to VCC -40 to +85 8 Un it V V V o C ns/V 1) VIN from 30% to 70% of VCC 3/9 74AC138 DC SPECIFICATIONS Symbol Parameter V CC (V) VIH High Level Input Voltage 3.0 4.5 5.5 VIL Low Level Input Voltage 3.0 4.5 5.5 VOH High Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 VOL Low Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 II ICC IOLD IOHD Input Leakage Current Quiescent Supply Current Dynamic Output Current (note 1, 2) 5.5 5.5 5.5 V I (*) = V IH or V IL VI = V IH or V IL (*) Test Con dition s Min.