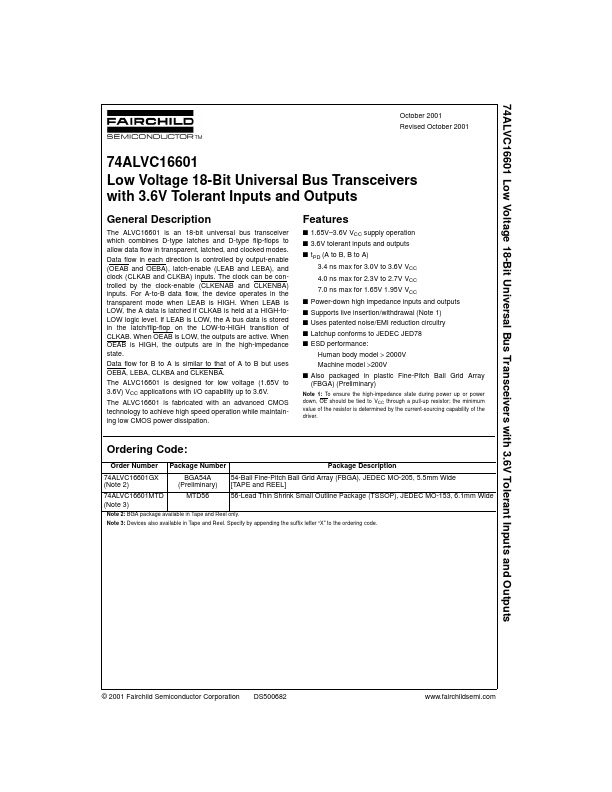

74ALVC16601

Description

The ALVC16601 is an 18-bit universal bus transceiver which bines D-type latches and D-type flip-flops to allow data flow in transparent, latched, and clocked modes. Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs.

Key Features

- 74ALVC16601MTD (Note

- L H B0 (Note

- L H B0 (Note