74LS09

Description

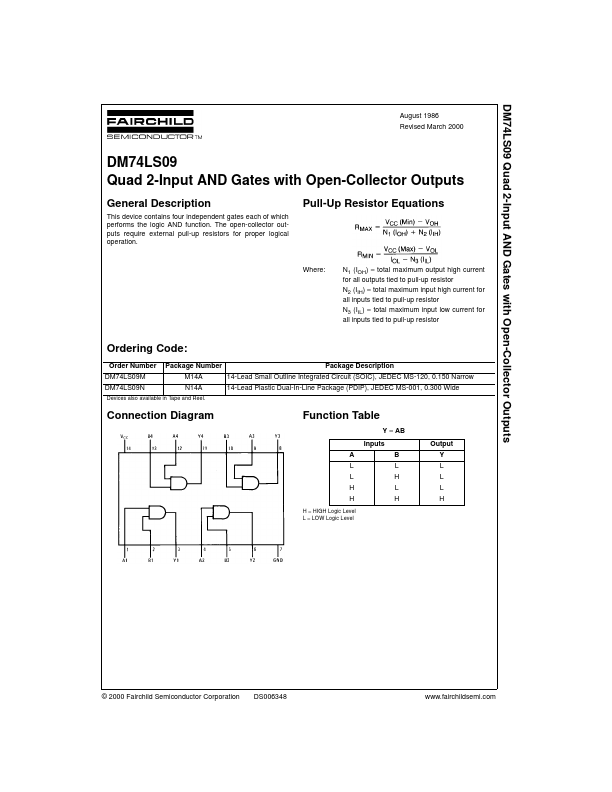

This device contains four independent gates each of which performs the logic AND function. The open-collector outputs require external pull-up resistors for proper logical operation.

Pull-Up Resistor Equations

Where:

N1 (IOH) = total maximum output high current for all outputs tied to pull-up resistor N2 (IIH) = total maximum input high current for all inputs tied to pull-up resistor N3 (IIL) = total maximum input low current for all inputs tied to pull-up resistor

Ordering Code:

Order Number DM74LS09M DM74LS09N Package Number M14A N14A Package Description

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel.

Connection Diagram

Function Table

Y = AB Inputs A L L H H

H = HIGH Logic Level L = LOW Logic Level

Output B L H L H Y L L L H

© 2000 Fairchild Semiconductor Corporation

DS006348

.fairchildsemi.

DM74LS09

Absolute Maximum...