74LS11

Overview

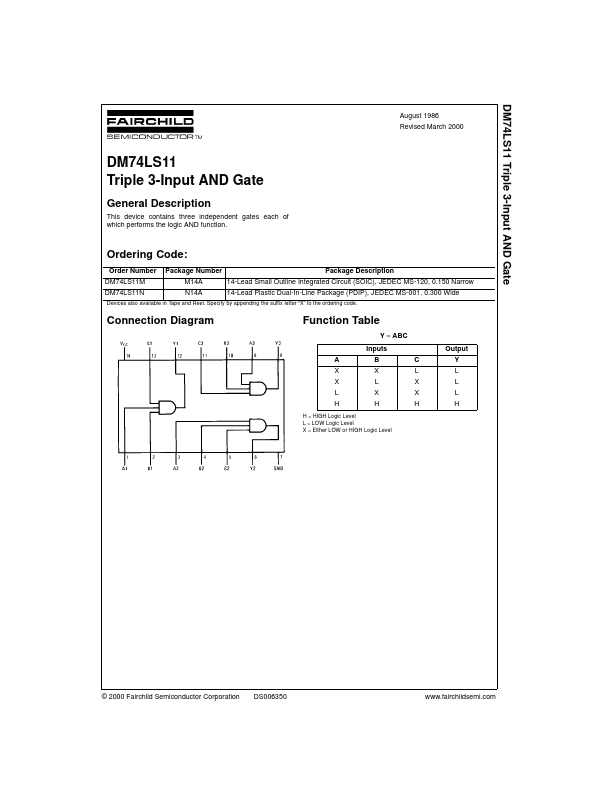

This device contains three independent gates each of which performs the logic AND function. Ordering Code: Order Number DM74LS11M DM74LS11N Package Number M14A N14A Package Description 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Devices also available in Tape and Reel.