74LS165

Description

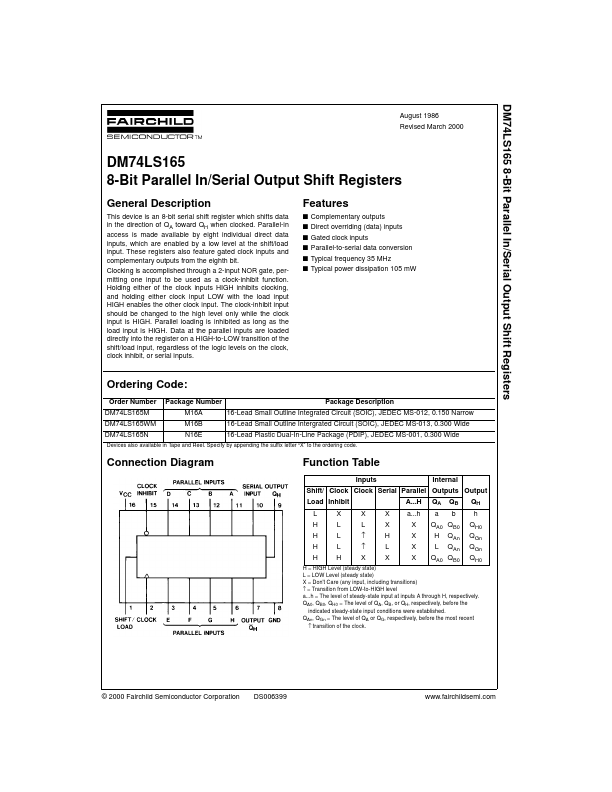

This device is an 8-bit serial shift register which shifts data in the direction of QA toward QH when clocked. Parallel-in access is made available by eight individual direct data inputs, which are enabled by a low level at the shift/load input.

Key Features

- Specify by appending the suffix letter “X” to the ordering code

- QA0, QB0, QH0 = The level of QA, QB, or QH, respectively, before the indicated steady-state input conditions were established

- QAn, QGn = The level of QA or QG, respectively, before the most recent ↑ transition of the clock

- © 2000 Fairchild Semiconductor Corporation DS006399 .fairchildsemi

- DM74LS165 Logic Diagram Timing Diagram Typical Shift, Load, and Inhibit Sequences .fairchildsemi